## SERVICE MANUAL

# HP 8340A SYNTHESIZED SWEEPER 10 MHz to 26.5 GHz

-

.

.

Page

#### **VOLUME 3 CONTENTS**

| Section Page                                                  | Section Page                                                                            |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| VIII SERVICE                                                  | Direct I/O Addressing                                                                   |

| Service Section Format                                        | Functions8-38Overall Instrument Troubleshooting8-41Repair Procedures8-55                |

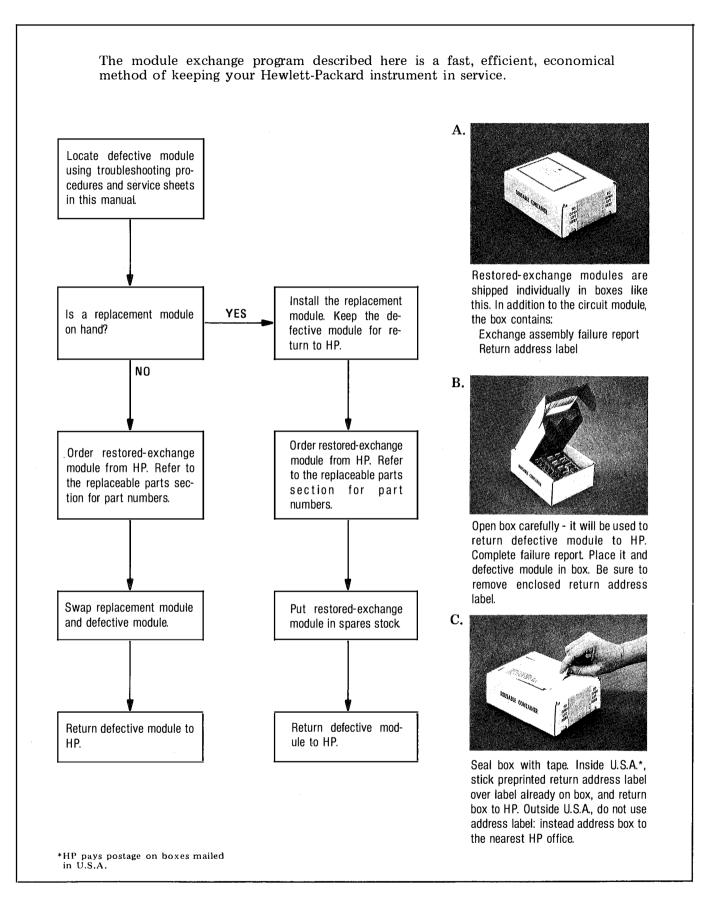

| 8340A Overall Instrument Theory 8-10<br>Calibration Constants | Module Exchange Program8-57After Service Safety Checks8-58Basic Component Symbology8-59 |

#### TABLES

æ

Table

| Table          | Page                                    |

|----------------|-----------------------------------------|

| 8A-1.          | Tools Supplied in Service Kit           |

| 8A-2.          | Equipment Not Supplied in               |

|                | Service Kit                             |

| 8A-3.          | Calibration Constants                   |

| 8A-4.          | I/O Devices                             |

| 8A-6.          | Omitted                                 |

| 8A-5.          | Direct I/O Data                         |

|                | Bit Information                         |

| 8 <b>B-</b> 1. | L4 Inductor Values and                  |

|                | Part Number                             |

| 8 <b>B-</b> 2. | Approximate Bias Voltage Levels for 100 |

|                | MHz Buffer Amplifier                    |

| 8B-3.          | Attenuation and Resistor Values for 100 |

|                | MHz OUT and 400 MHz OUT 8-113           |

| 8 <b>B-</b> 4. | Approximate Bias Levels for Quadrupler |

|----------------|----------------------------------------|

|                | and 400 MHz Amplifier                  |

| 8 <b>B-</b> 5. | Divider Operations                     |

| 8 <b>B-</b> 6. | Increment Decoder Operation 8-127      |

| 8C-1.          | 20-30 Loop Parameters 8-164            |

| 8C-2.          | 20-30 Loop Frequency Range vs.         |

|                | Divider Configuration                  |

| 8C-3.          | FET Switch Programming Table 8-188     |

| 8D-1.          | Sensitivity of 20-30 SWP Line 8-297    |

| 8D <b>-</b> 2. | Bias Voltages on A49 under Different   |

|                | Loop Conditions                        |

| 8D-3.          | Instrument Frequency vs.               |

|                | YO Frequency                           |

| 8E-1.          | Motherboard Wiring List                |

#### SAFETY CONSIDERATIONS

#### GENERAL

This product and related documentation must be reviewed for familiarization with safety markings and instructions before operation. This product has been designed and tested in accordance with international standards.

#### SAFETY SYMBOLS

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual (refer to Table of Contents).

Indicates hazardous voltages.

Indicates earth (ground) terminal.

**WARNING** The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in personal injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

CAUTION

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAU-TION sign until the indicated conditions are fully understood and met.

#### SAFETY EARTH GROUND

This is a Safety Class I product (provided with a protective earthing terminal). An uninterruptible safety earth ground must be provided from the main power source to the product input wiring terminals, power cord, or supplied power cord set. Whenever it is likely that the protection has been impaired, the product must be made inoperative and be secured against any unintended operation.

#### **BEFORE APPLYING POWER**

Verify that the product is configured to match the available main power source per the input power configuration instructions provided in this manual.

If this product is to be energized via an autotransformer, make sure the common terminal is connected to the neutral (grounded) side of mains supply.

#### SERVICING

WARNING

Any servicing, adjustment, maintenance, or repair of this product must be performed only by qualified personnel.

Adjustments described in this manual may be performed with power supplied to the product while protective covers are removed. Energy available at many points may, if contacted, result in personal injury.

Capacitors inside this product may still be charged even when disconnected from its power source.

To avoid a fire hazard, only fuses with the required current rating and of the specified type (normal blow, time delay, etc.) are to be used for replacement.

## REFERENCE GUIDE TO SERVICE DOCUMENTATION

/

|                     | # /                                                                  |          | ,         | /        | /             | 7    | 7            | s/    | 7   |                     | 7  |

|---------------------|----------------------------------------------------------------------|----------|-----------|----------|---------------|------|--------------|-------|-----|---------------------|----|

|                     | definition                                                           |          | /         | in allon | ŝ             | /    | Contechor 10 |       | /   | Power Section Panel |    |

|                     |                                                                      | /        | 3         |          | ?/š           | \$/5 | ]/\$         |       |     |                     | §/ |

| / ギ                 | · /                                                                  | /-       |           | nin in   | 3/            | \$`/ | elle         |       | \$/ | Power of            |    |

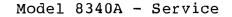

| A1                  | Alpha Display                                                        | <u>/</u> | <u>/*</u> | <u> </u> | <u>//~</u>    | 2    | <u>79</u>    | /«    | 79  |                     |    |

| A2                  | Display Driver                                                       | 33       |           | 4        |               |      |              | •     |     |                     |    |

| A3<br>A4            | Display Processor<br>Not Assigned                                    | 33       |           |          | 27            |      | 1.1          | .•    | 1   |                     |    |

| A5                  | Keyboard                                                             | 35       |           |          |               |      |              | •     |     |                     |    |

| A6<br>A7            | Keyboard Interface<br>Lower Keyboard                                 | 35<br>35 |           |          |               |      |              | •     |     |                     |    |

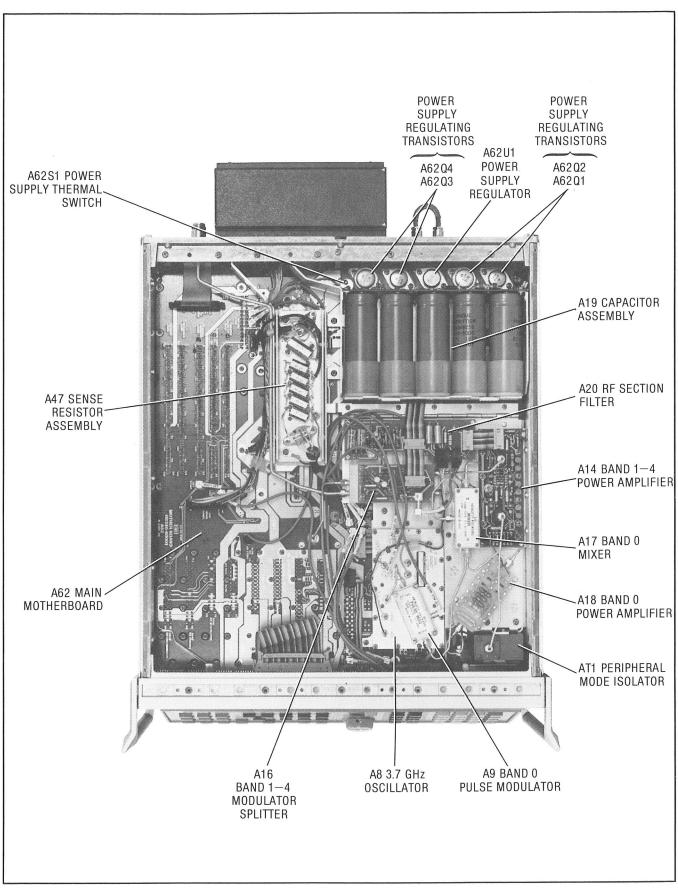

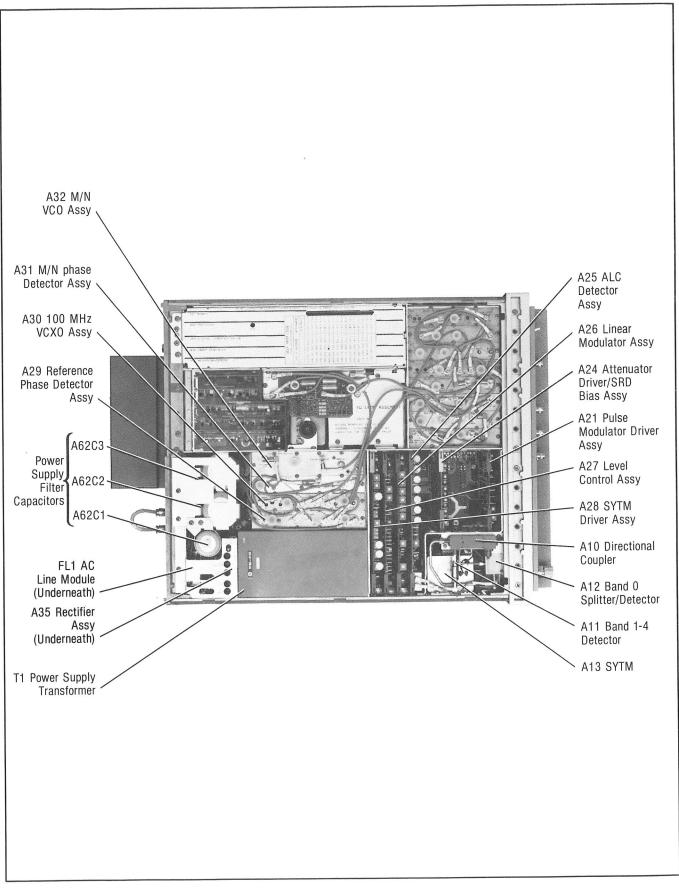

| A8<br>A9            | 3.7 GHz Öscillator<br>Band O Pulse Modulator                         | 57<br>56 |           |          | 1. 2          |      |              |       | •   | 8                   |    |

| A10                 | Directional Coupler                                                  | 32       | S.        | ·        | ina'<br>Gr    |      | 2<br>2 - 2   |       |     |                     |    |

| A11<br>A12          | Band 1-4 Detector<br>Band 0 Splitter/Detector                        | 3t<br>34 |           |          | anti<br>Tanat |      |              |       |     |                     |    |

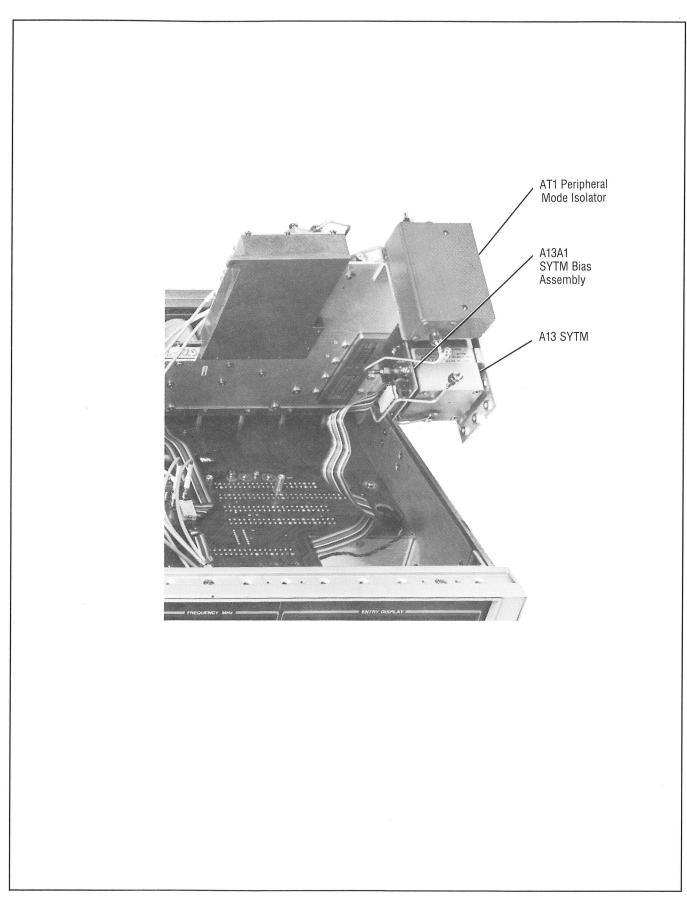

| A13                 | SYTM (Switched YIG Tuned Multiplier)                                 | 30       |           |          |               |      | 1.1          |       |     |                     |    |

| A14<br>A15          | Band 1-4 Power Amplifier<br>Band 0 Low Pass Filter                   | 53<br>52 |           |          |               |      |              |       |     |                     |    |

| A16                 | Band 1-4 Modulator/Splitter                                          | 51       |           |          |               |      |              |       | •   |                     |    |

| A17<br>A18          | Band O Mixer<br>Band O Power Amplifier                               | 54<br>55 |           | 1        |               |      |              |       |     |                     |    |

|                     | [이 물론] 관련 이 같은 것이 있는 것이 같이 많이 했다.                                    | 60       | 1         |          |               |      |              |       | •   |                     |    |

| A19<br>A20          | Capacitor Assembly<br>RF Section Filter                              | 48<br>50 |           |          |               |      | 1            |       | •   | •                   |    |

| A21                 | Pulse Modulator Driver                                               | 29       |           |          |               |      |              |       | •   |                     |    |

| A22<br>A23          | Not Assigned<br>Not Assigned                                         | -        |           |          |               |      |              |       |     |                     |    |

| A24<br>A25          | Attenuator Driver/SRO Bias<br>ALC Detector                           | 28<br>27 |           |          |               |      | 111          | 1.1   | •   |                     |    |

| A26                 | Linear Modulator                                                     | 26       |           |          |               |      |              |       |     |                     |    |

| A27<br>A28          | Level Control<br>SYTM Driver                                         | 25<br>24 |           |          |               |      | 1.1          |       |     |                     |    |

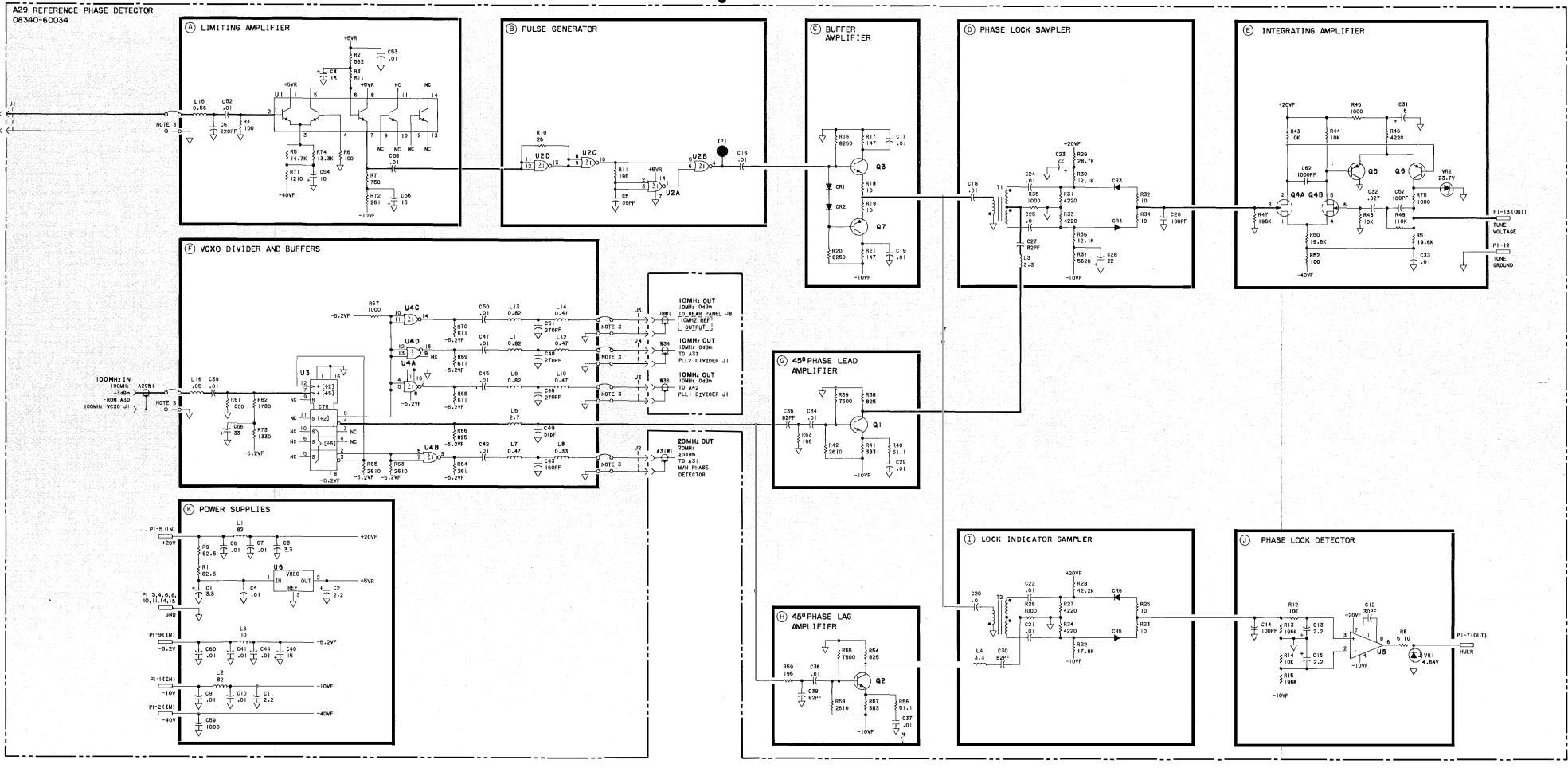

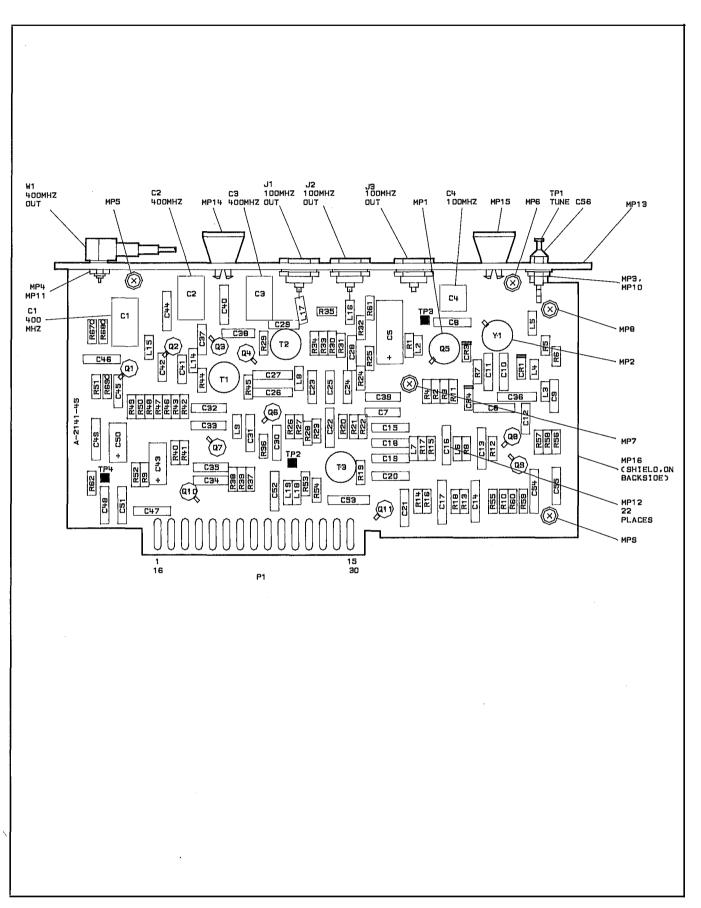

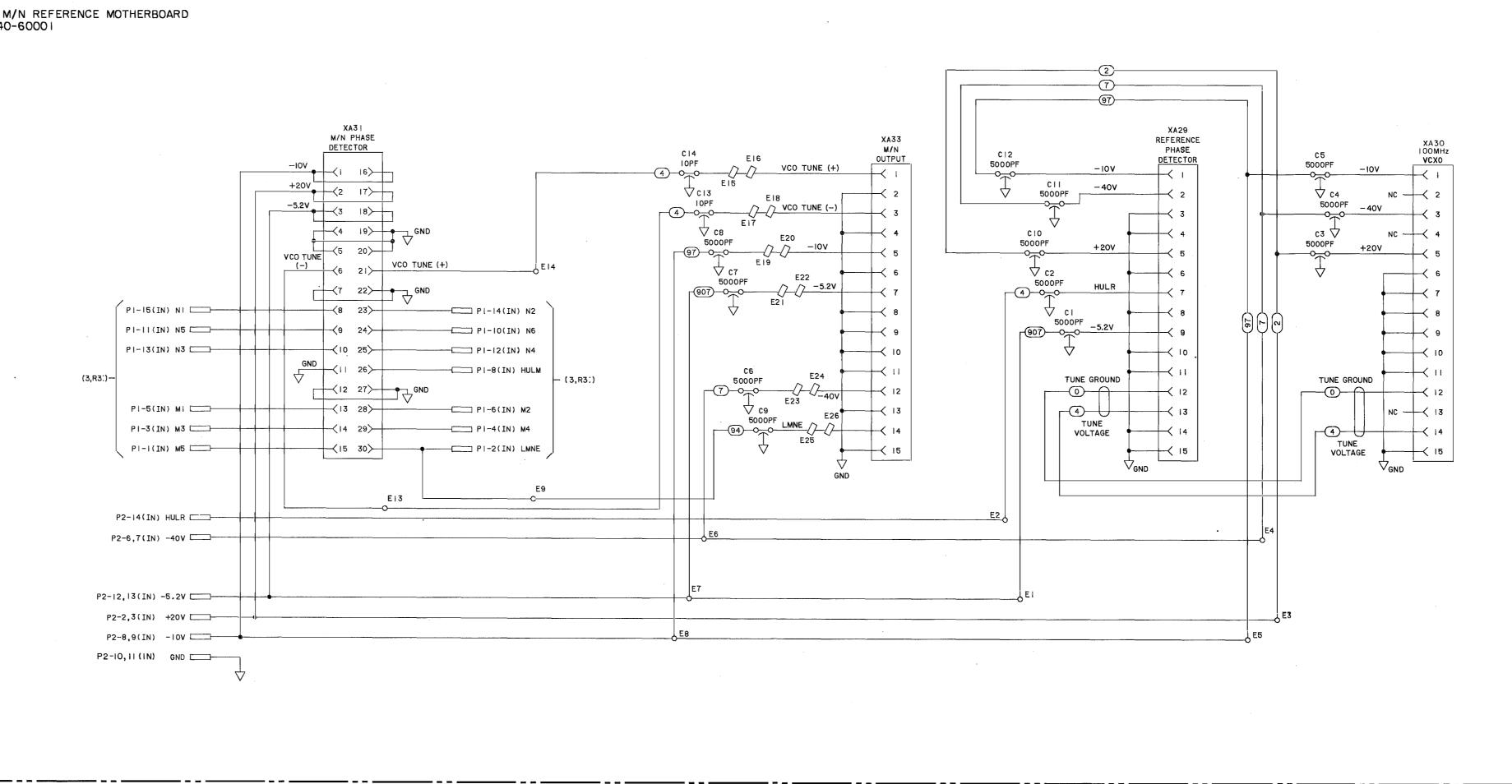

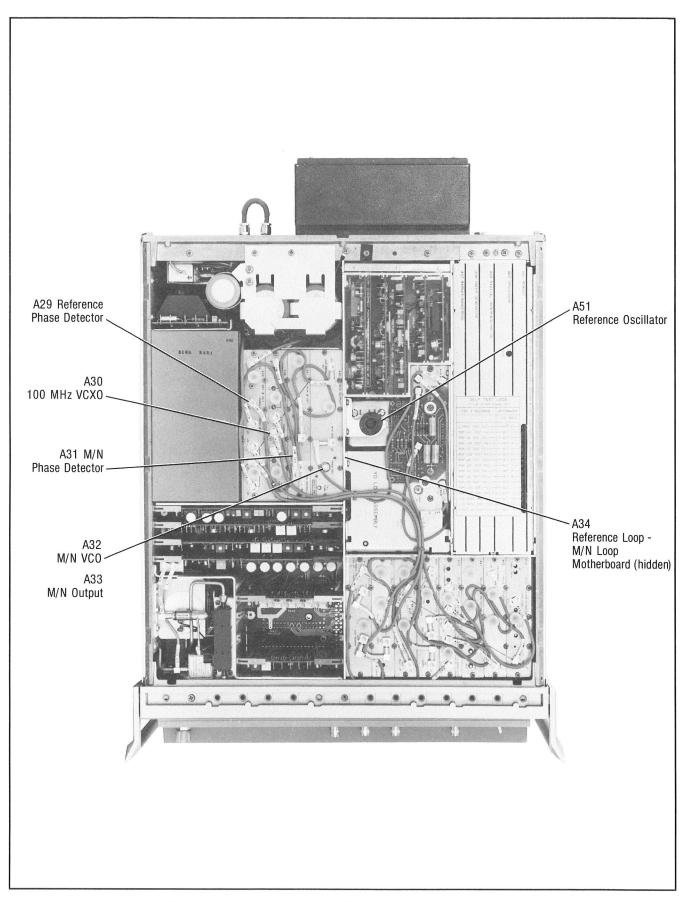

| A29                 | Reference Phase Detector                                             | 12       | •         |          |               |      |              |       |     |                     |    |

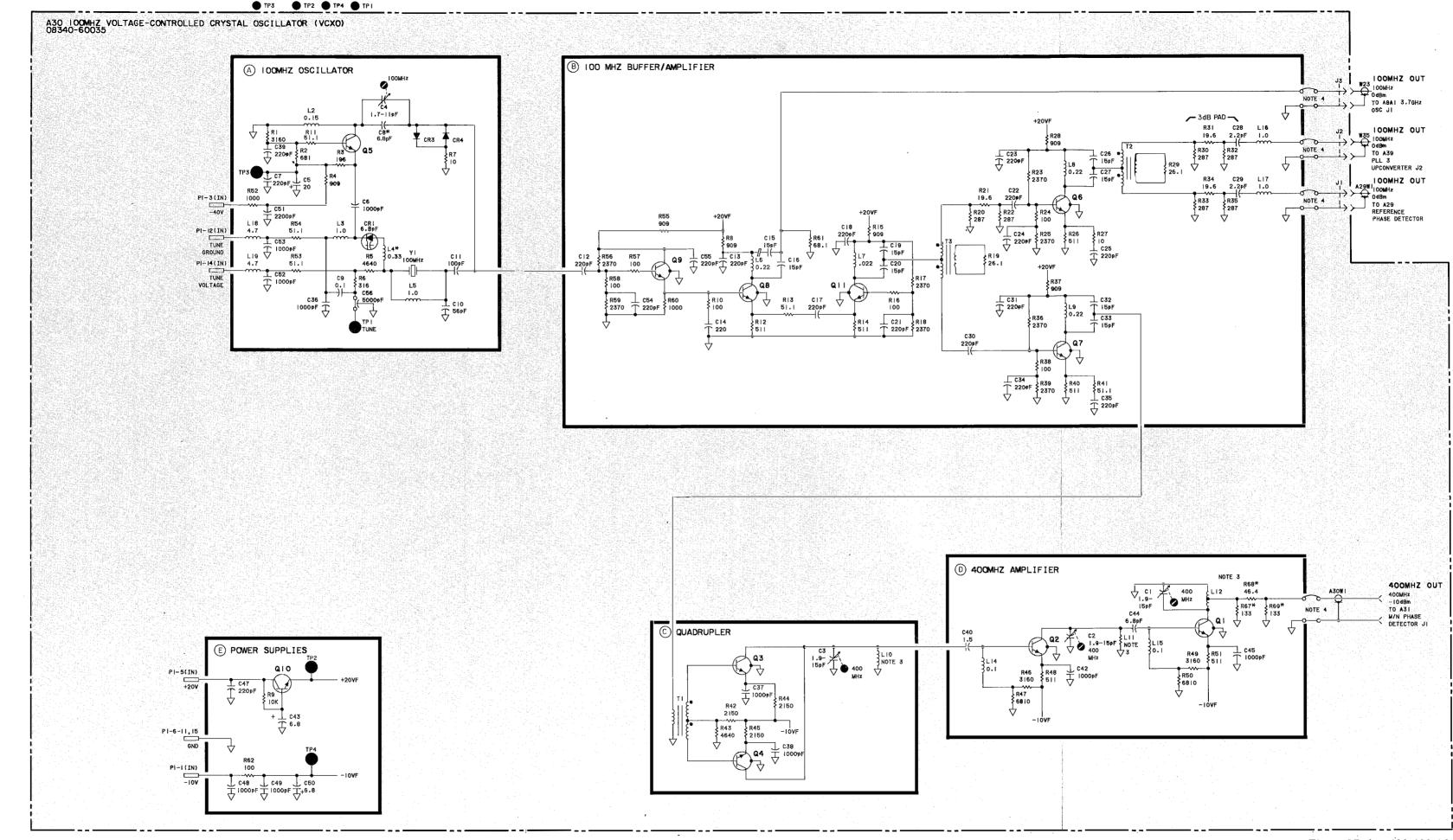

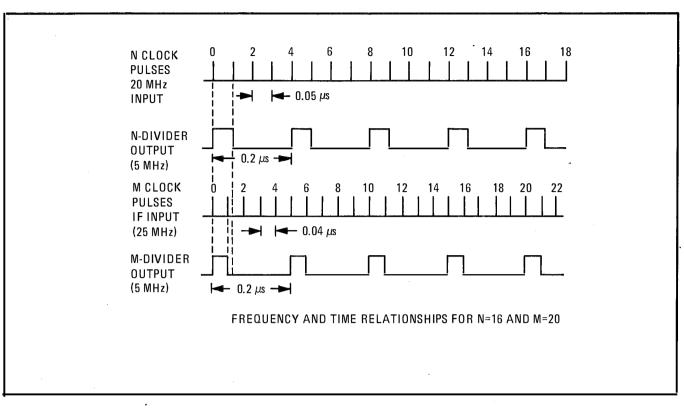

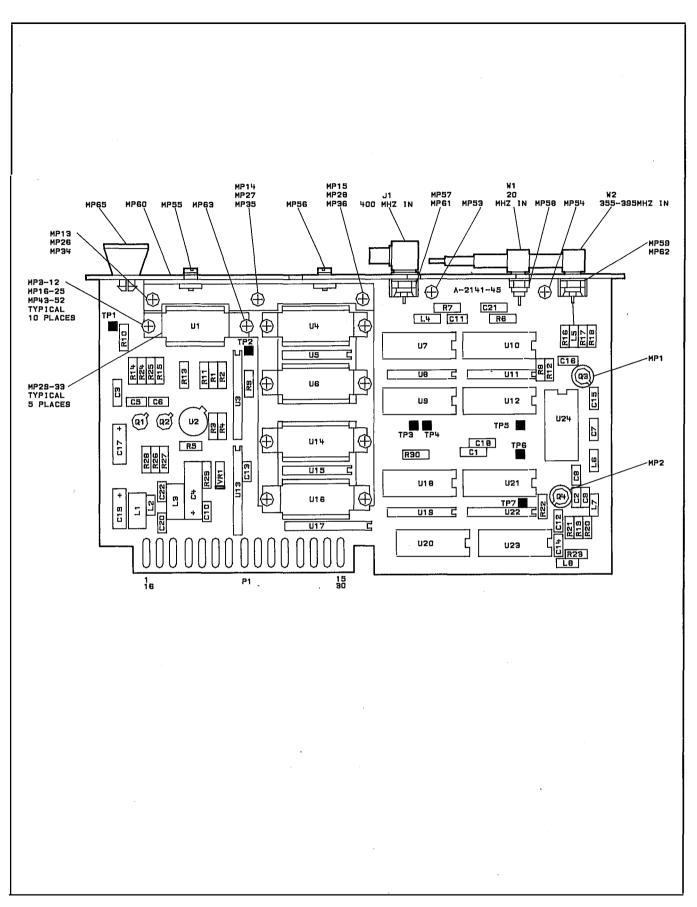

| A30<br>A31          | 100 MHz VCXO (Voltage Controlled Crystal Osc.)<br>M/N Phase Detector | 13<br>14 | •         |          |               |      |              |       |     |                     |    |

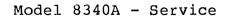

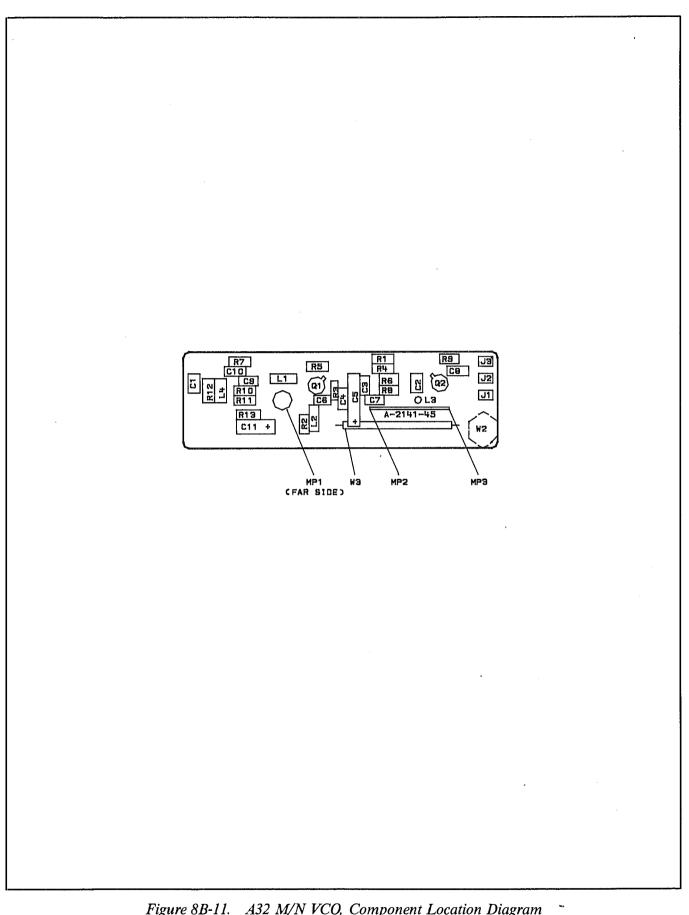

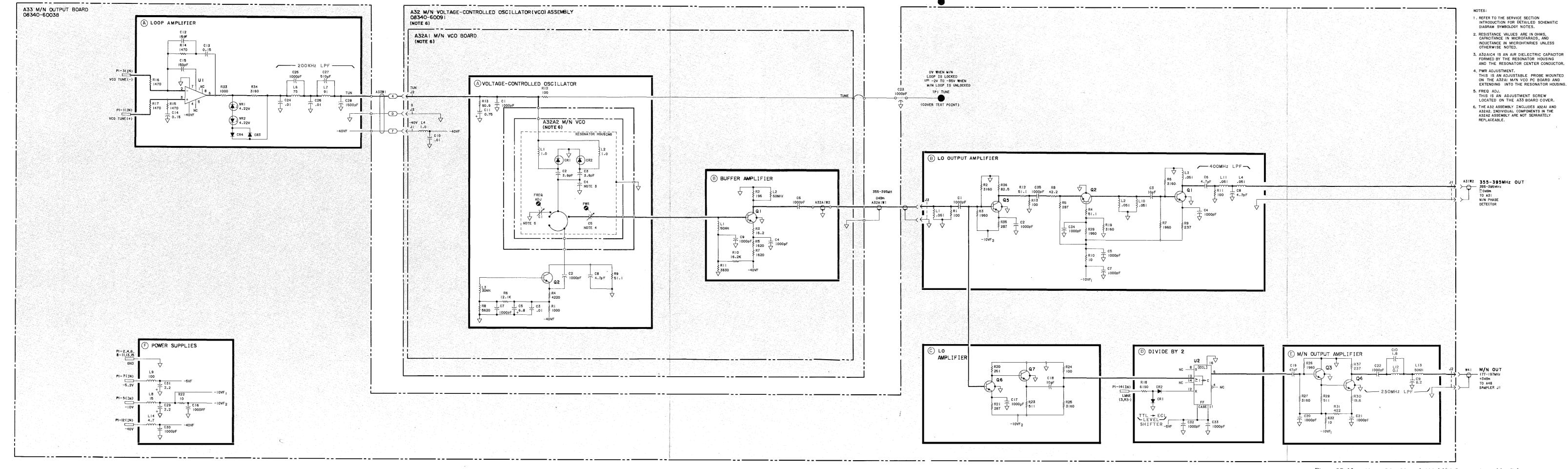

| A32                 | M/N VCO (Voltage Controlled Osc.)                                    | 15       | •         |          |               |      |              |       |     |                     |    |

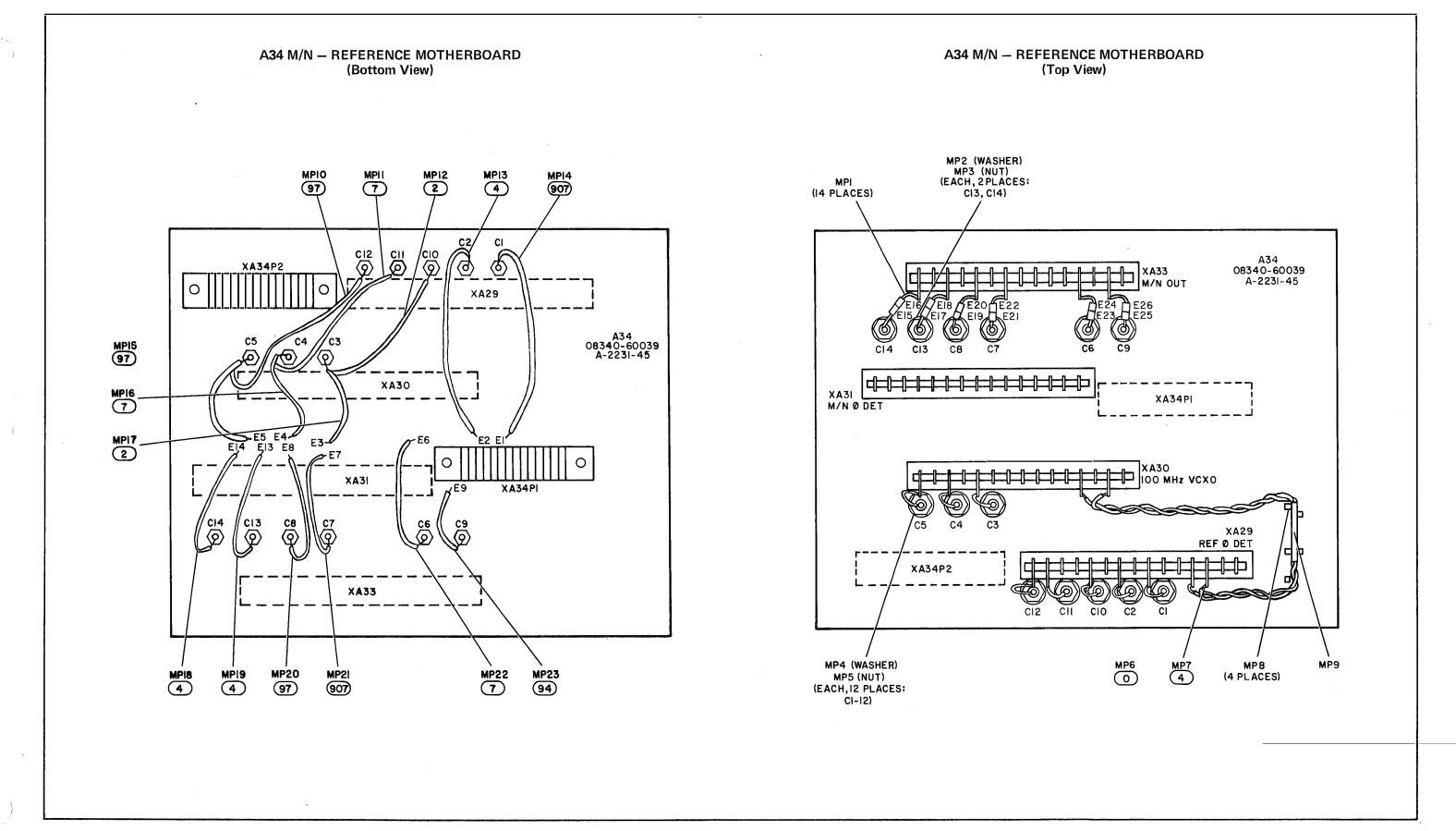

| A <b>3</b> 3<br>A34 | M/N Output<br>Reference-M/N Motherboard                              | 15<br>5  | •         | . P      |               |      | <br>         |       |     |                     |    |

| A35                 | Rectifier                                                            | 4<br>36  | - ·       |          |               |      |              | •     |     | •                   |    |

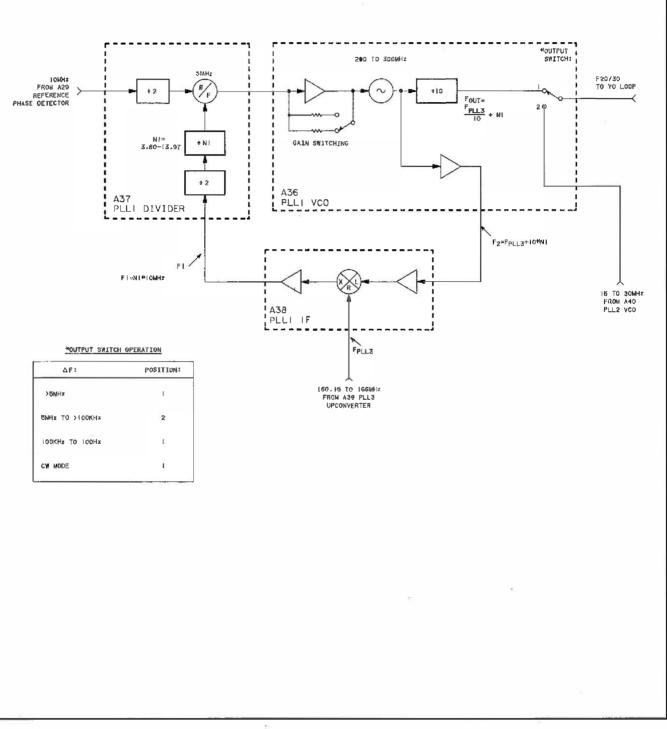

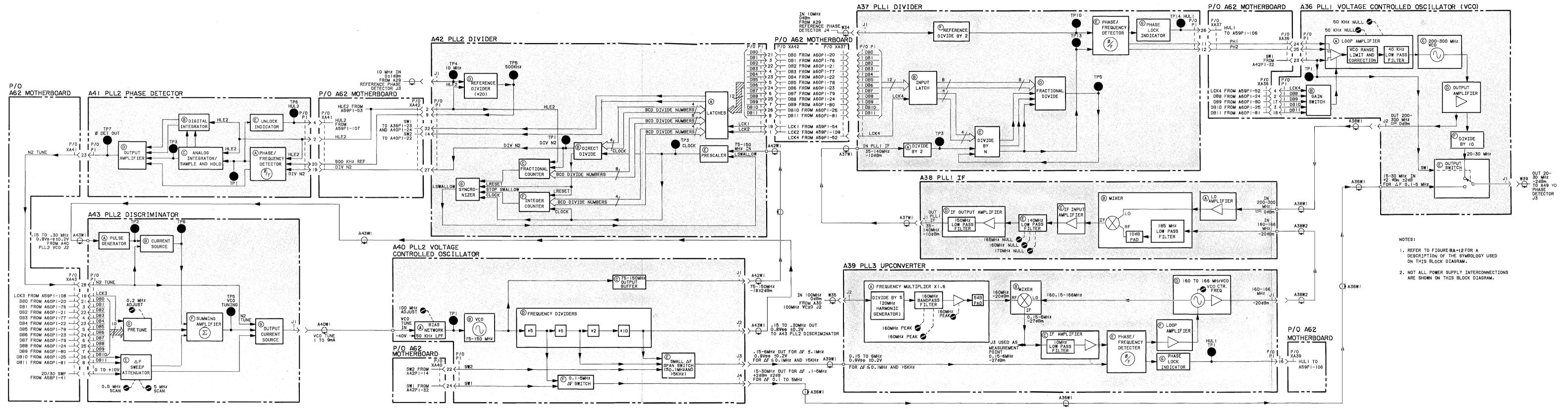

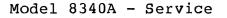

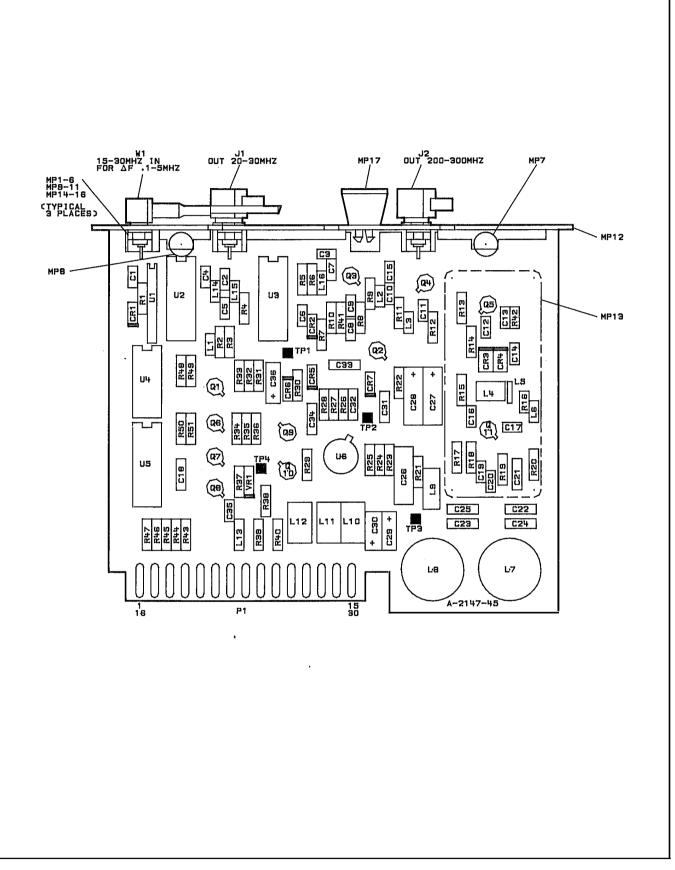

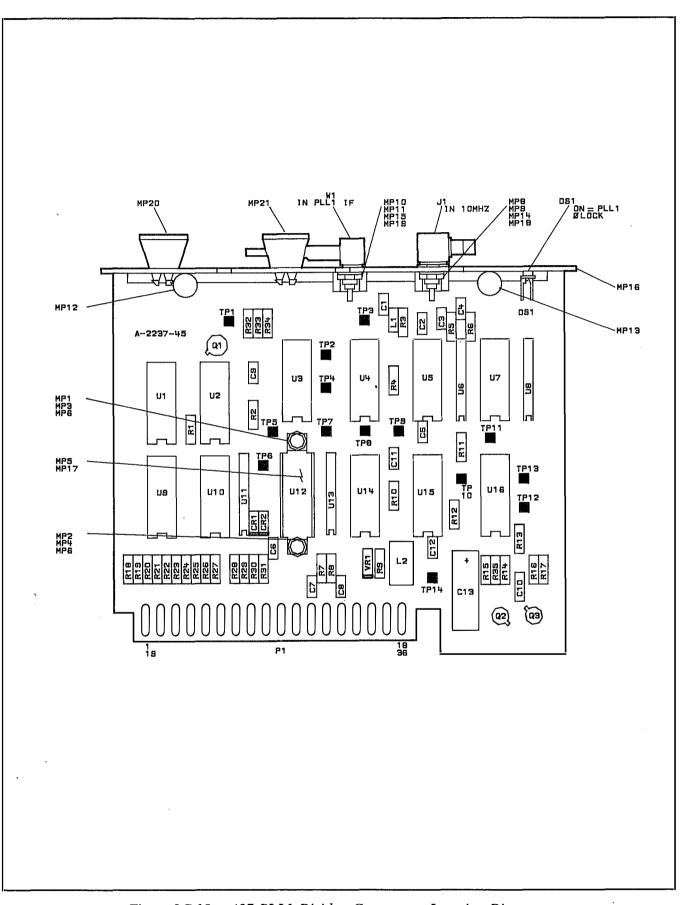

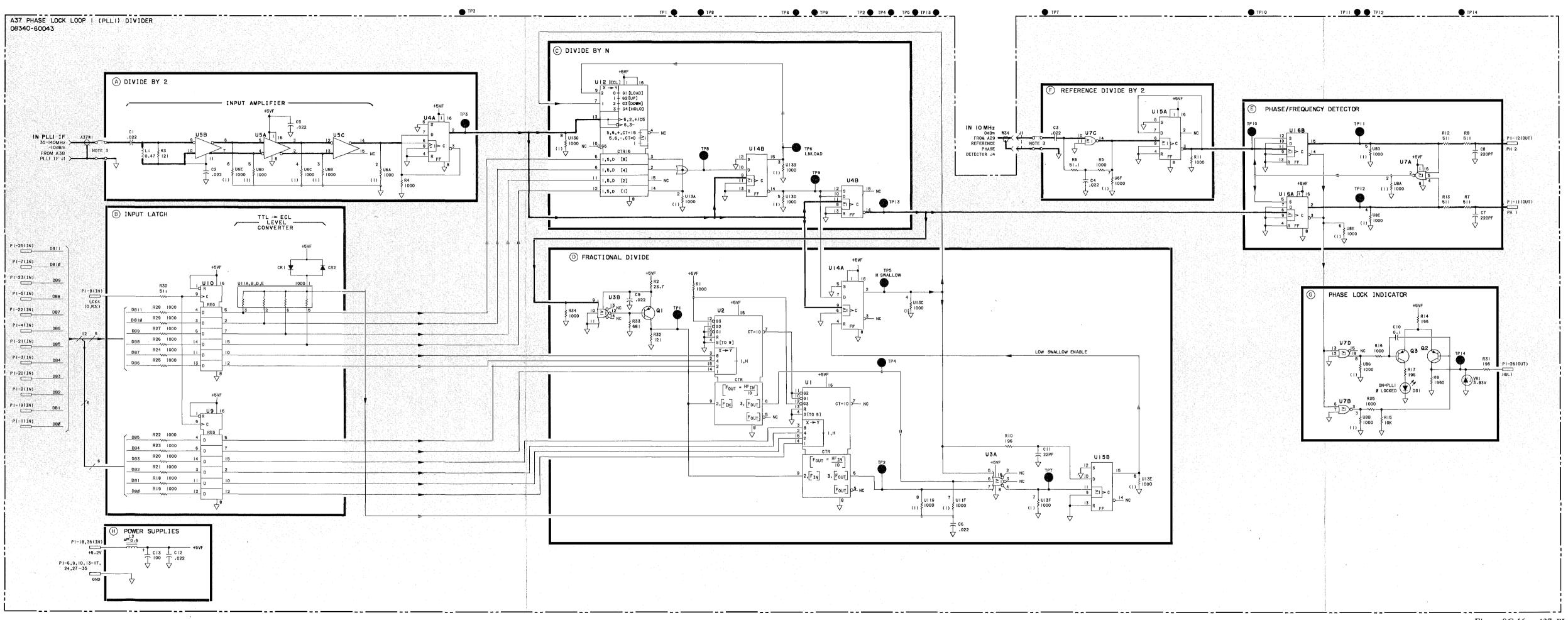

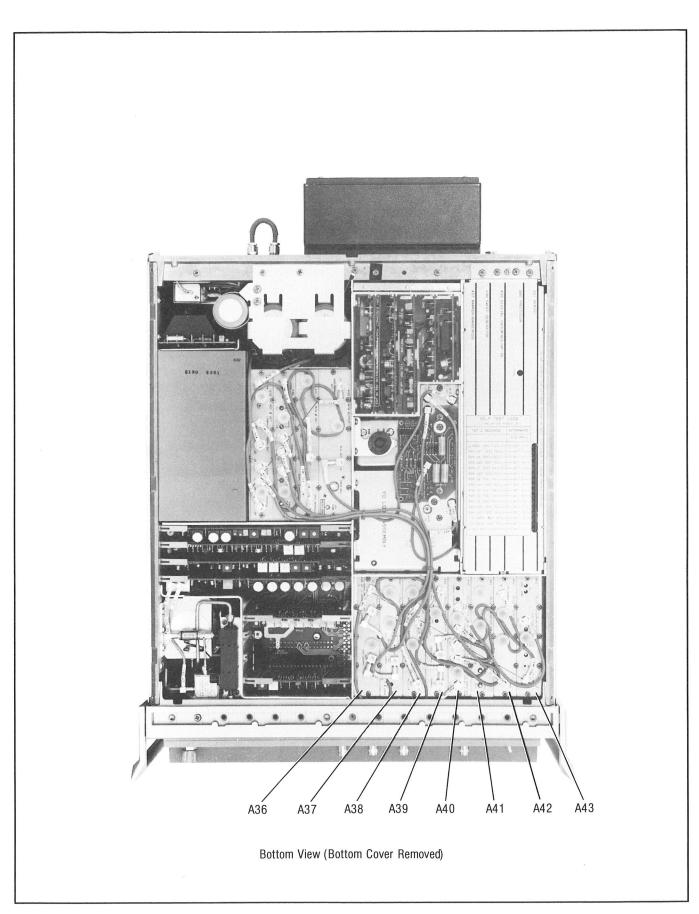

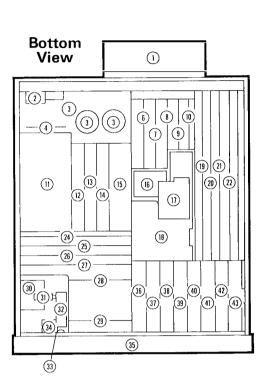

| A36<br>A37          | PLL1 VCO (Voltage Controlled Osc.)<br>PLL1 Divider                   | 37       |           | •        |               |      |              |       |     |                     |    |

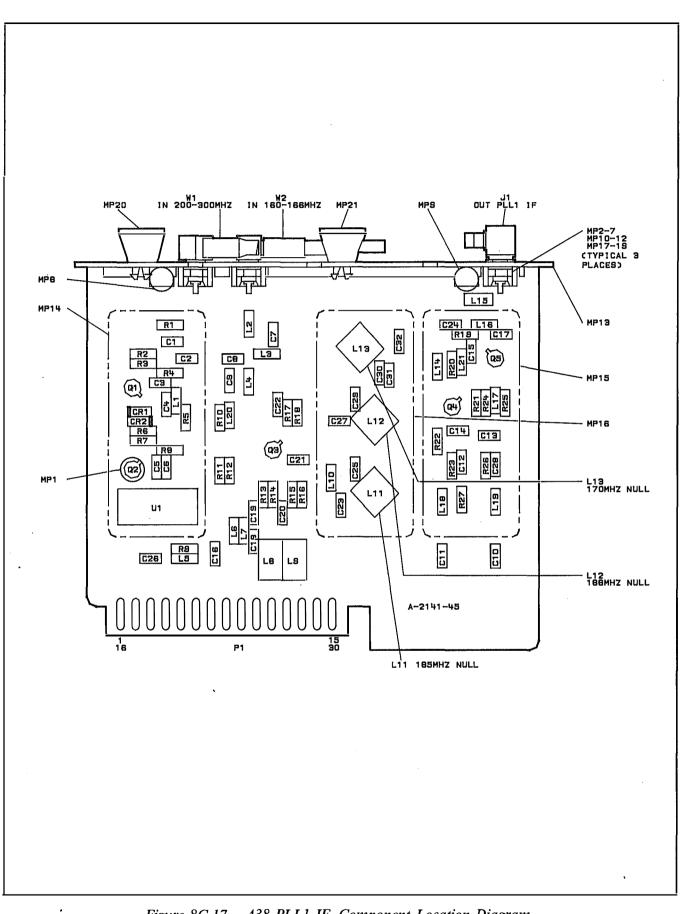

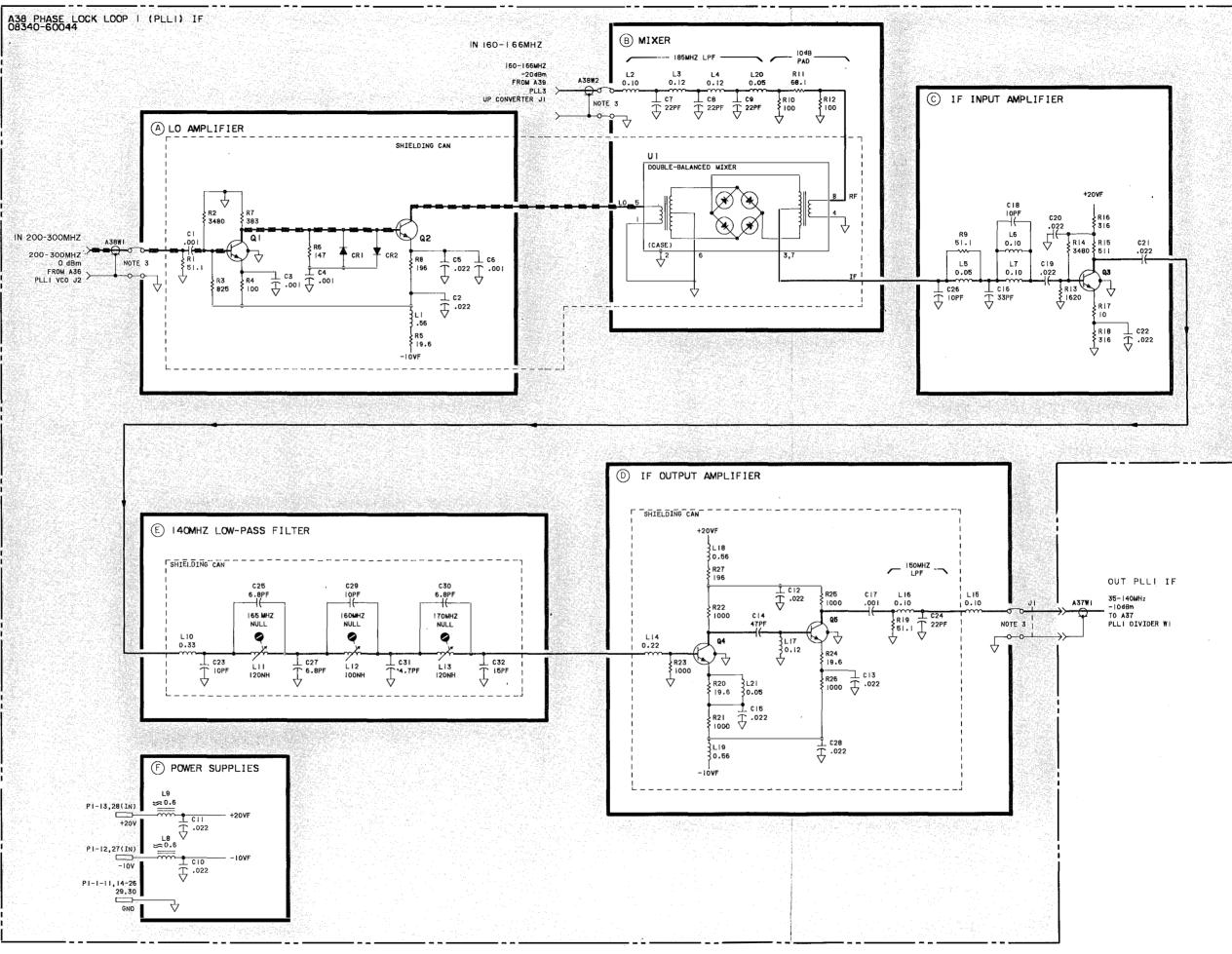

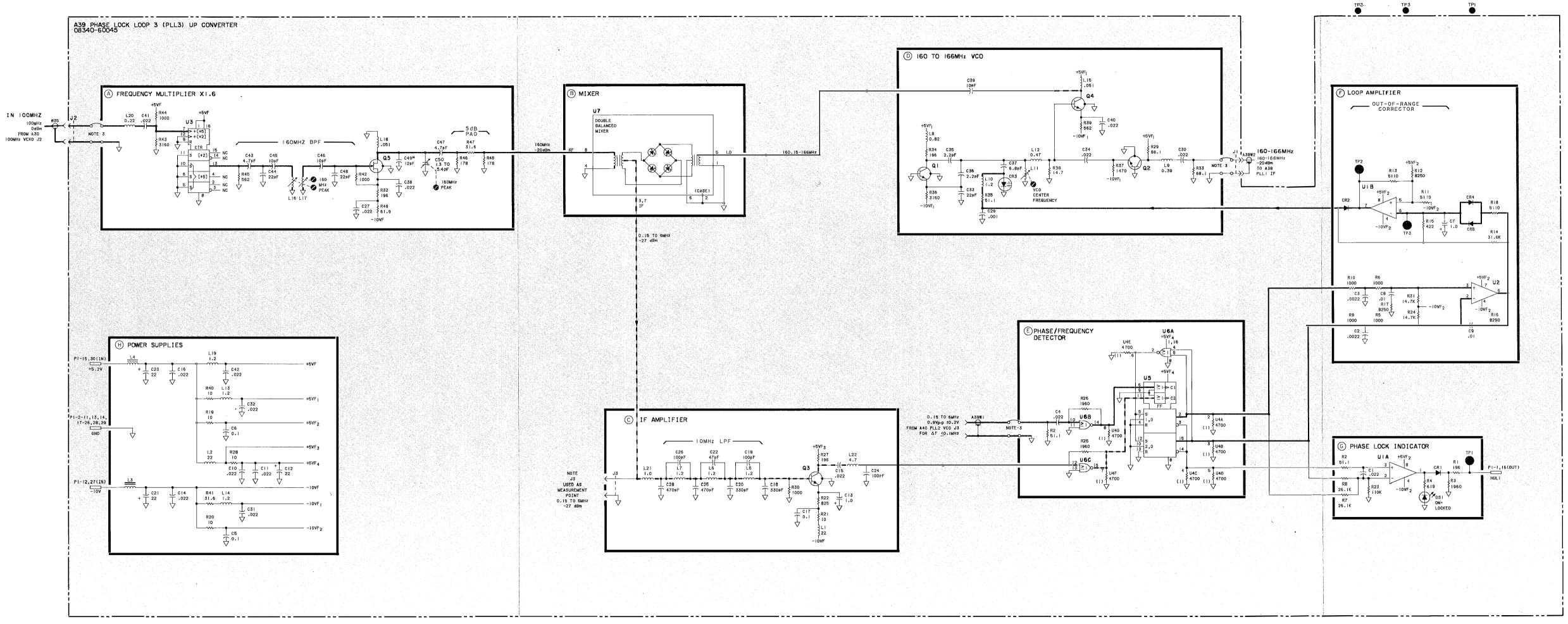

| A38<br>A39          | PLL1 IF<br>PLL3 Upconverter                                          | 38<br>39 |           | •        |               |      |              |       |     |                     |    |

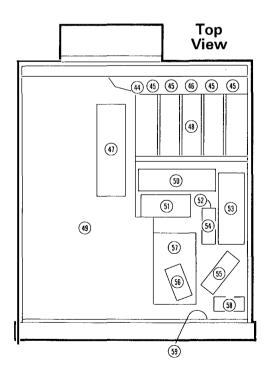

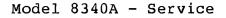

| A40                 | PLL2 VCO (Voltage Controlled Osc.)                                   | 40       |           | •        | 1.4 A.<br>A.  |      |              |       |     |                     |    |

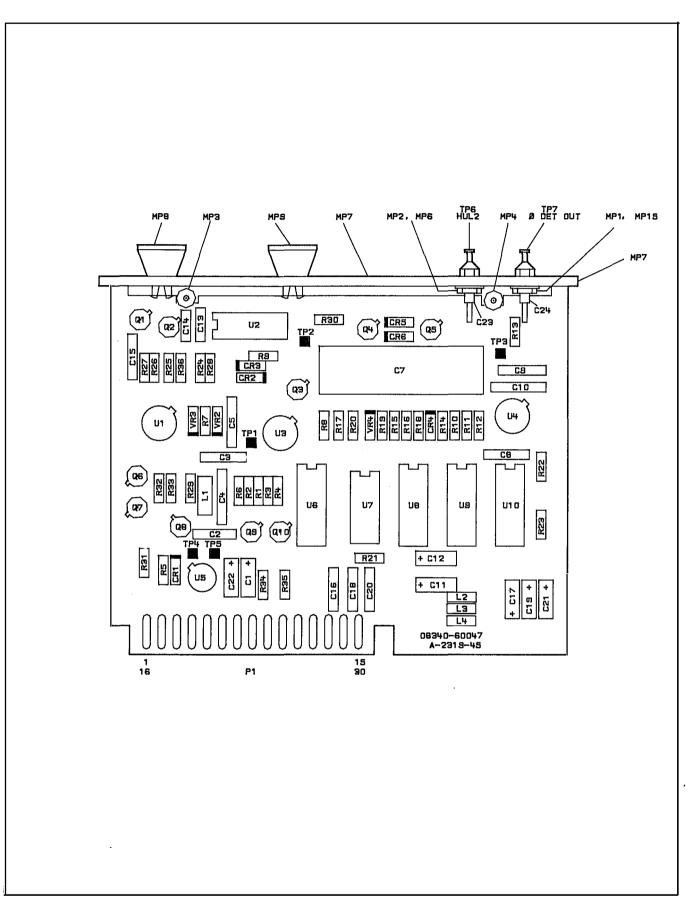

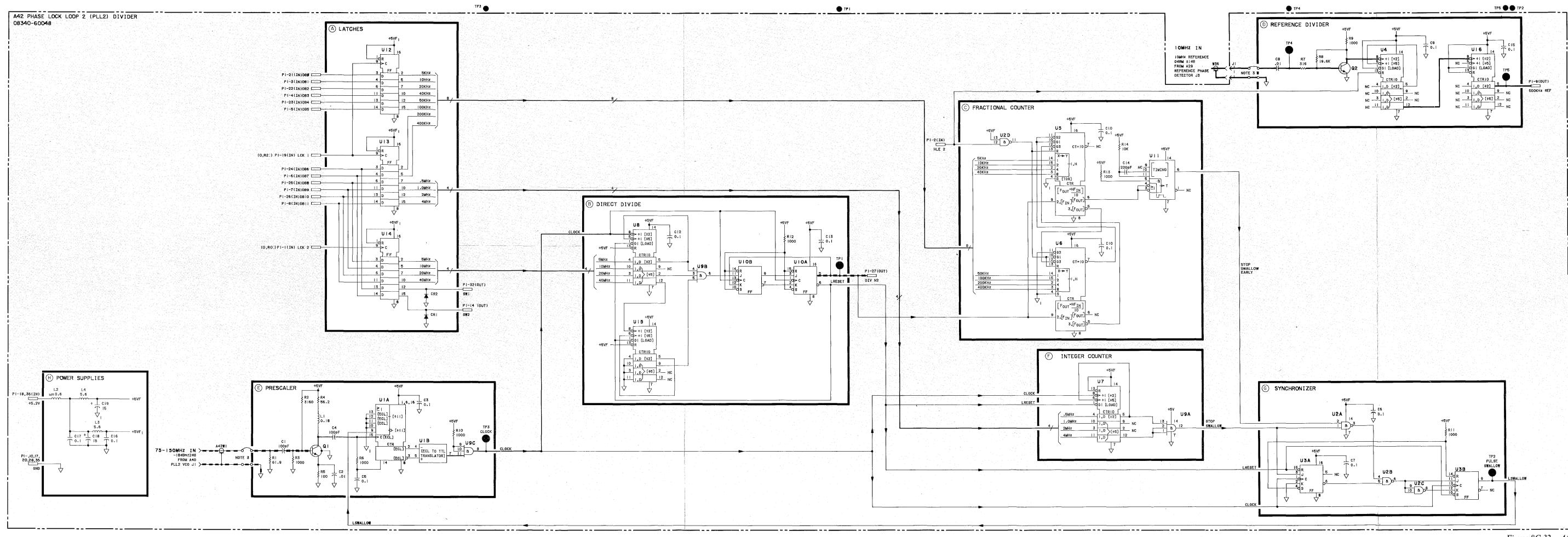

| A41<br>A42          | PLL2 Phase Detector<br>PLL2 Divider                                  | 41<br>42 |           |          |               |      |              |       |     |                     |    |

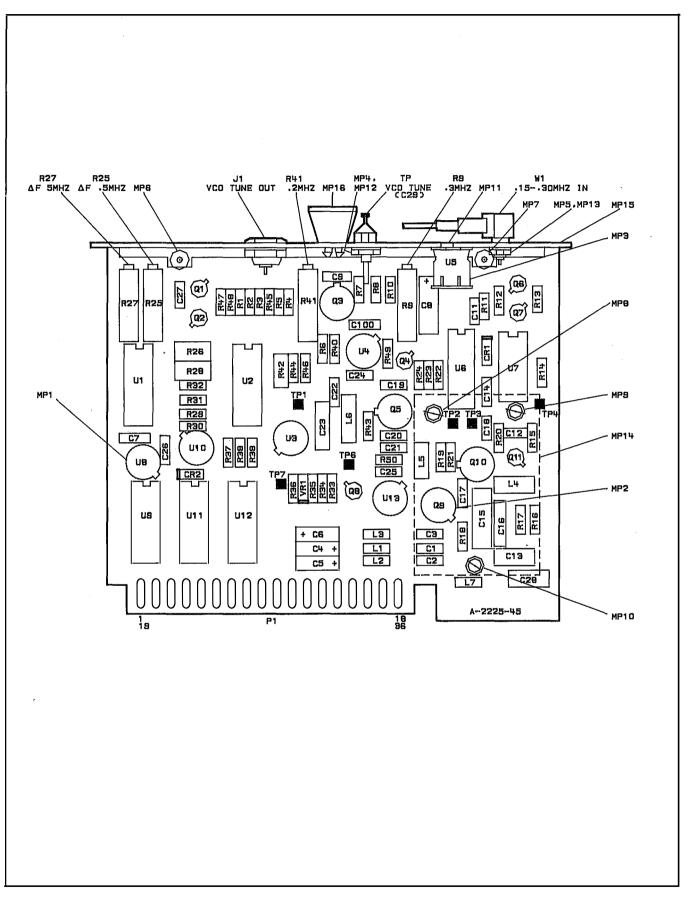

| A43                 | PLL2 Discriminator                                                   | 43       | · . ·     | •        | - 14 - 1<br>  |      |              |       | 1.0 |                     |    |

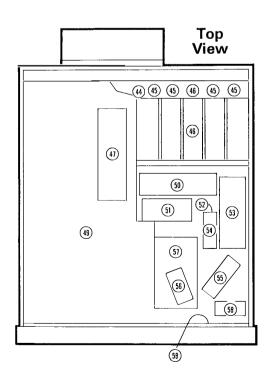

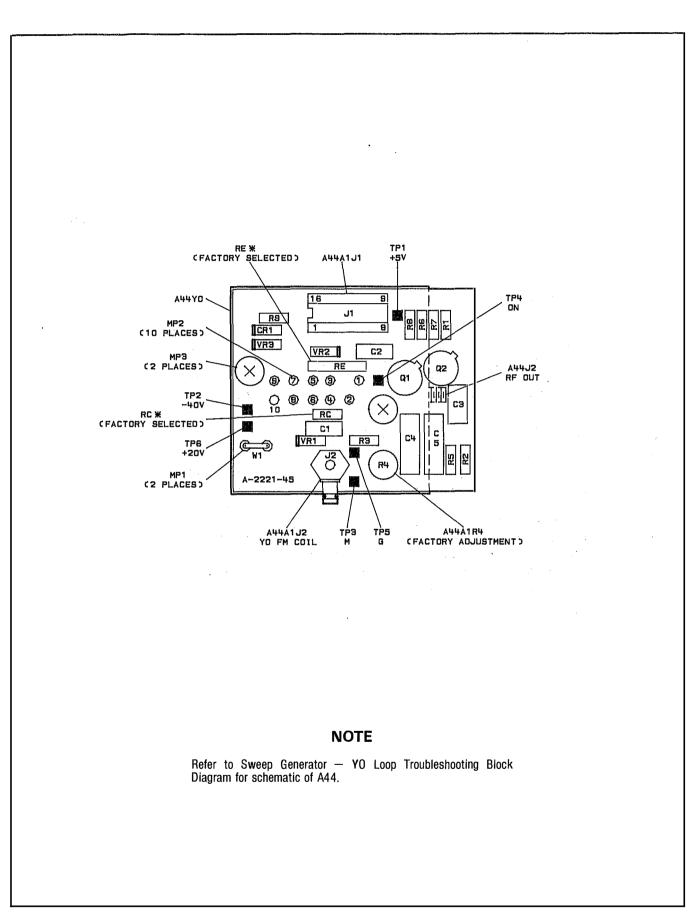

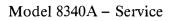

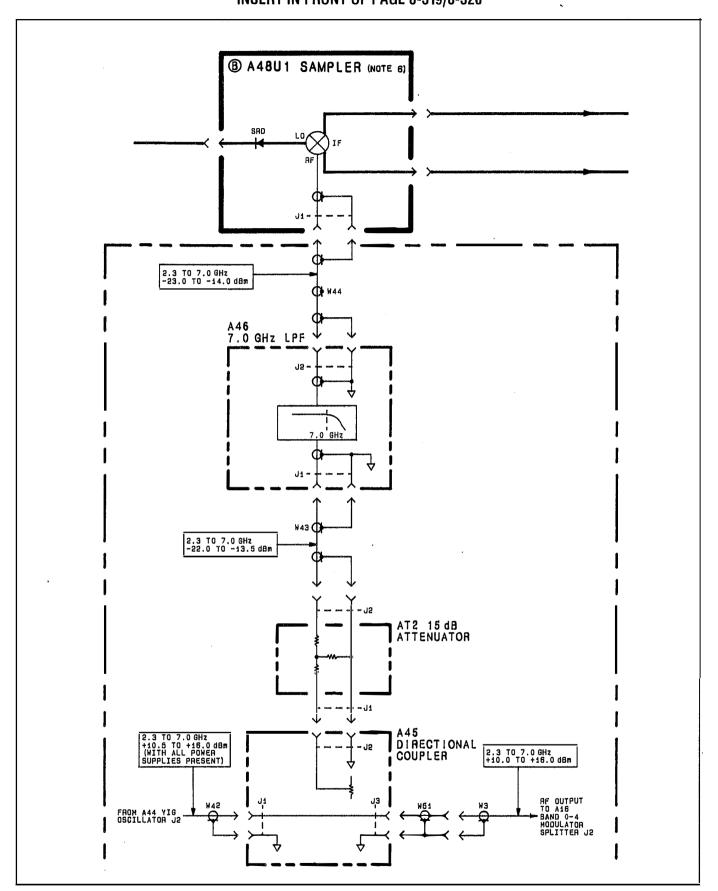

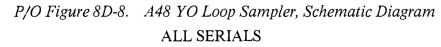

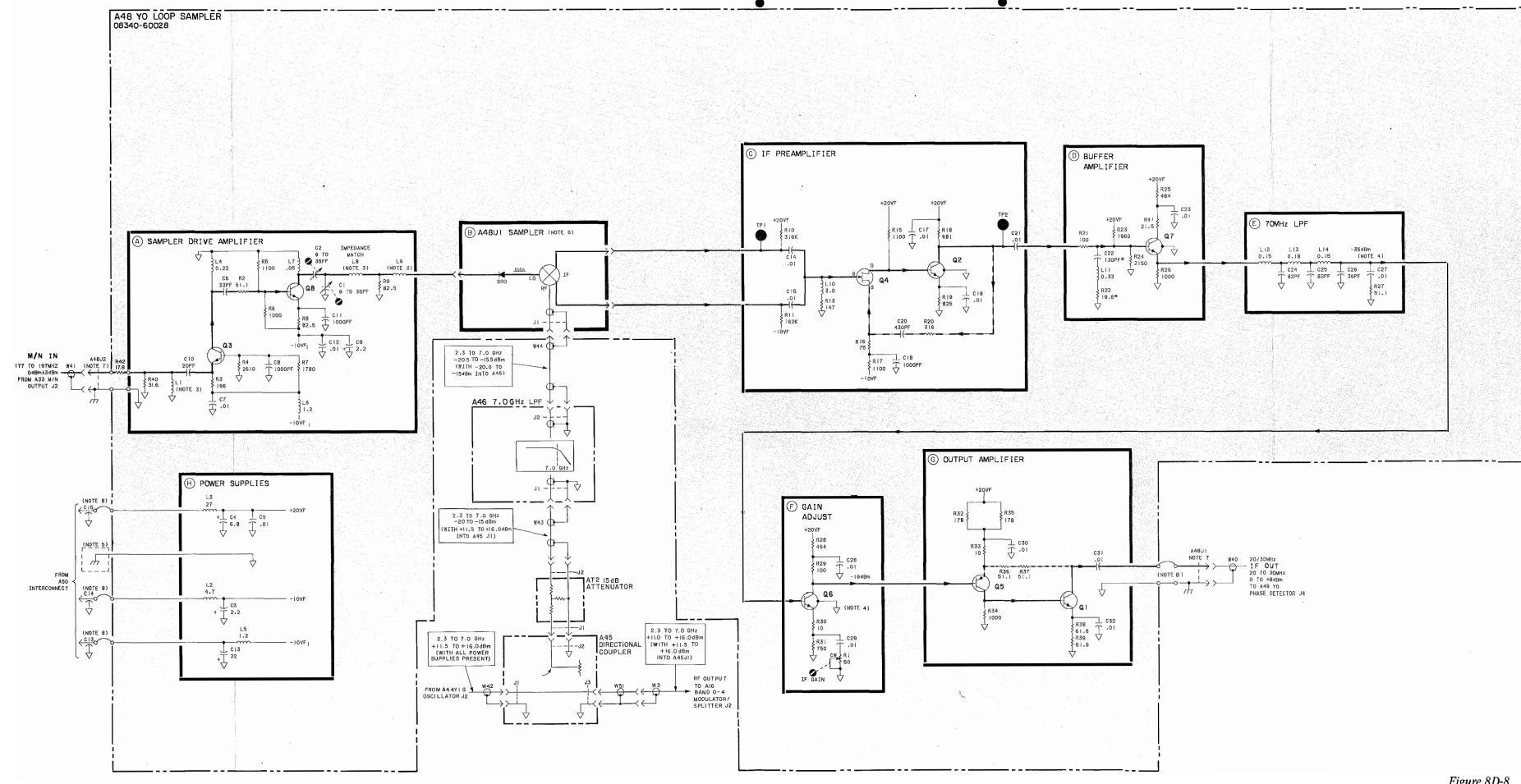

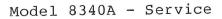

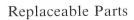

| A44<br>A45          | YIG Oscillator (YO)<br>Directional Coupler                           | 18<br>18 |           |          | •             |      |              |       |     |                     |    |

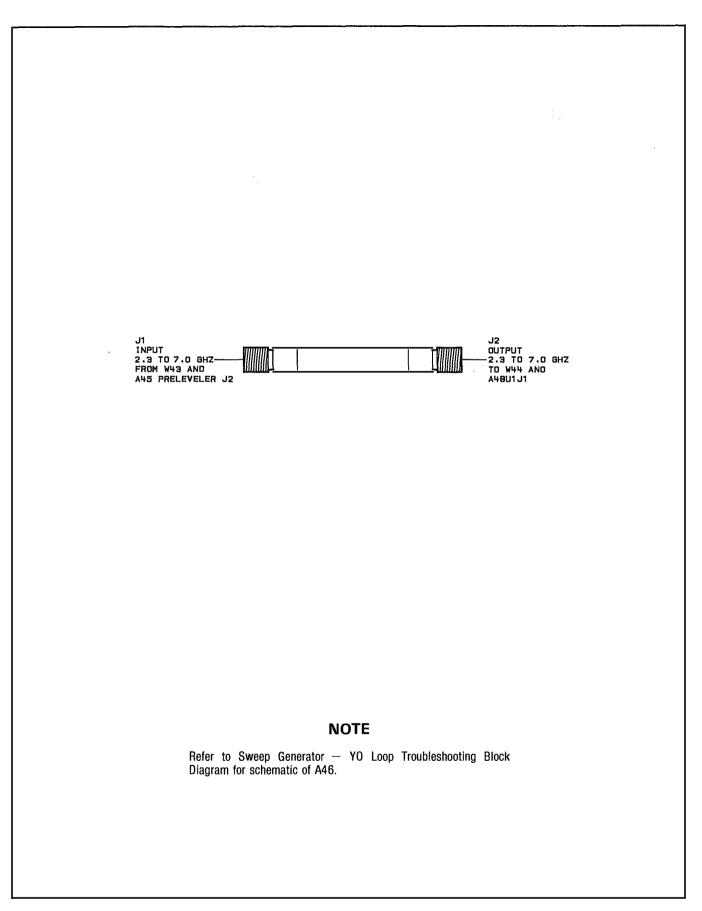

| A46                 | 7 GHz Low Pass Filter                                                | 18       |           |          | •             |      |              |       |     |                     |    |

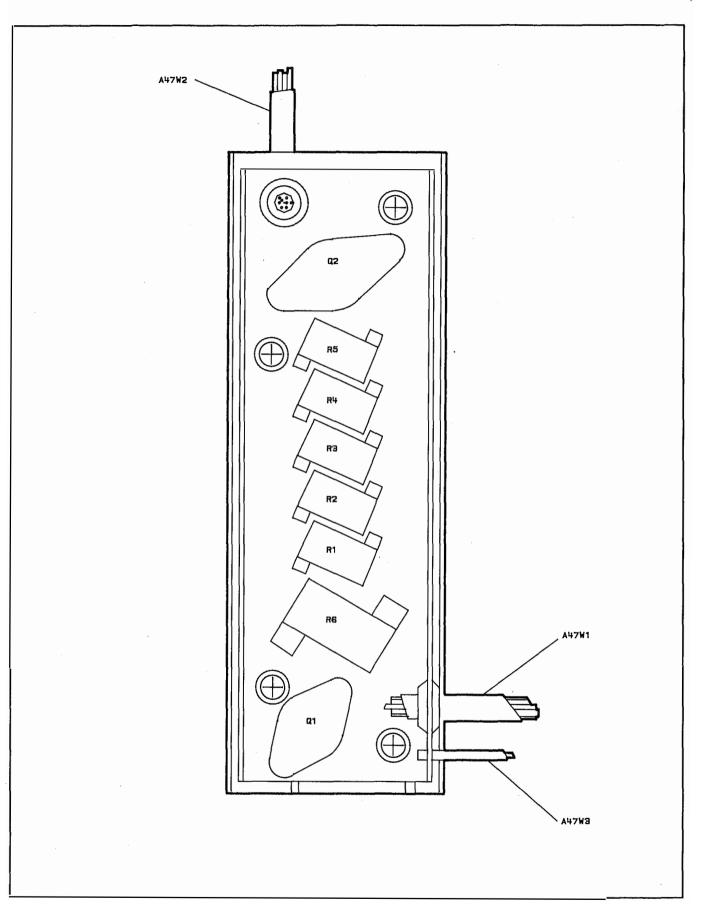

| A47                 | Sense Resistor Assembly (YO circuit)<br>(SYTM circuit)               | 47<br>47 |           |          | •             |      |              |       | •   |                     |    |

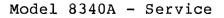

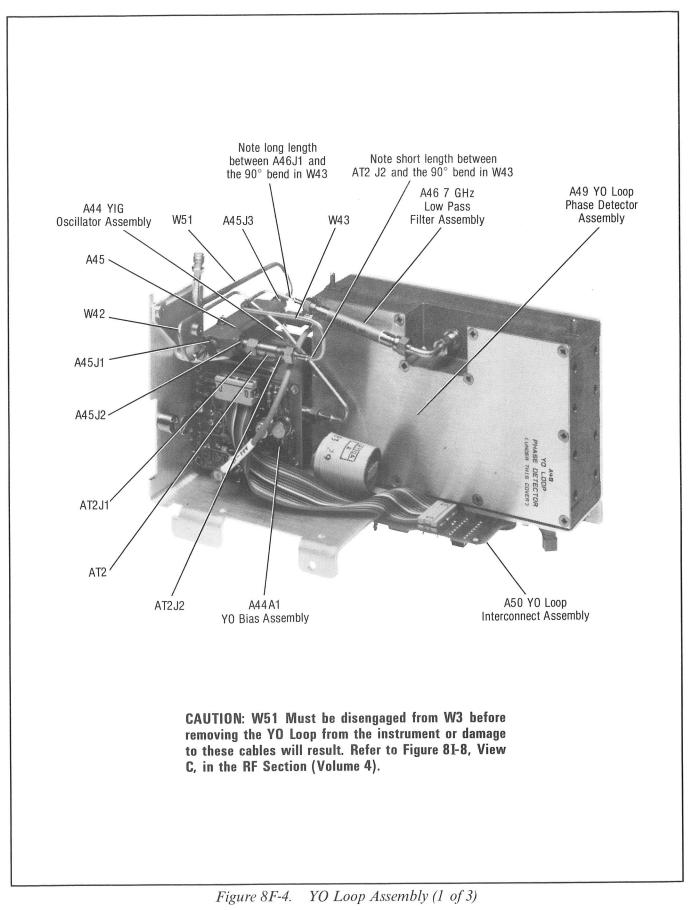

| A48<br>A49          | YO Loop Sampler<br>YO Loop Phase/Detector                            | 18<br>18 |           |          | •             |      |              |       |     |                     |    |

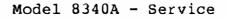

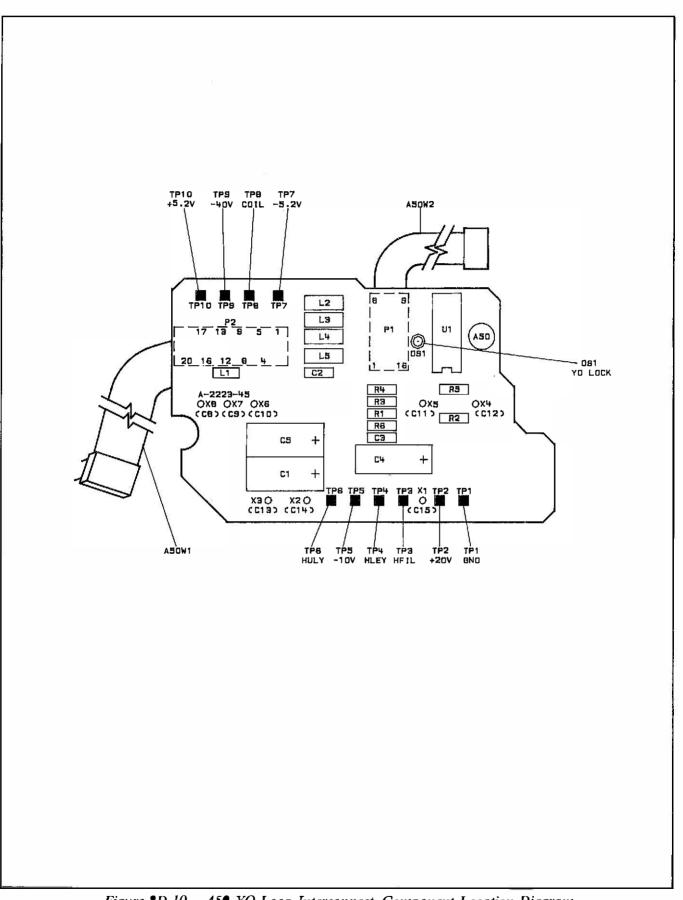

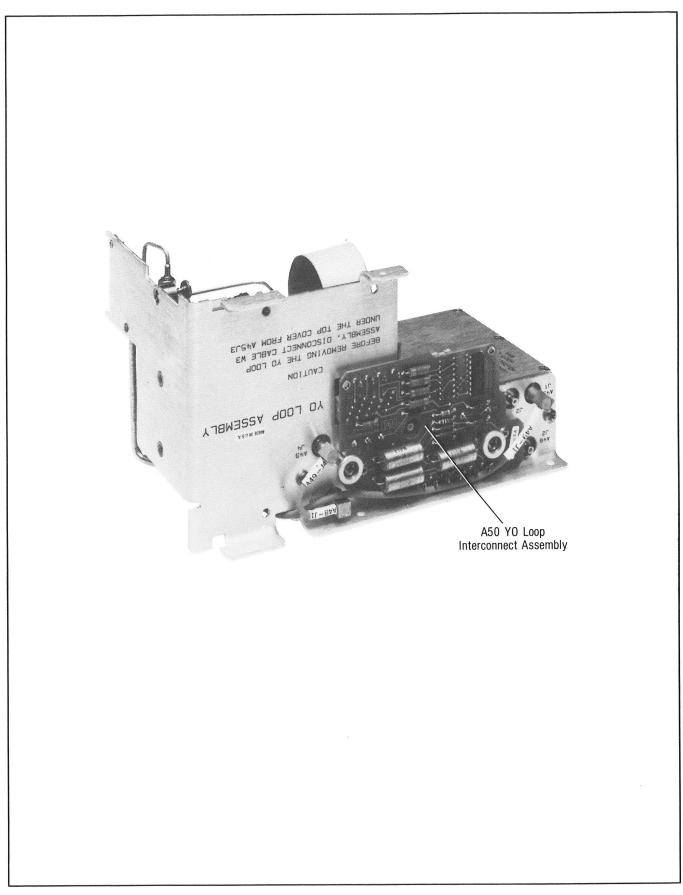

| A50                 | YO Loop Interconnect                                                 | . t7     | 1.1       |          | •             |      |              |       |     |                     |    |

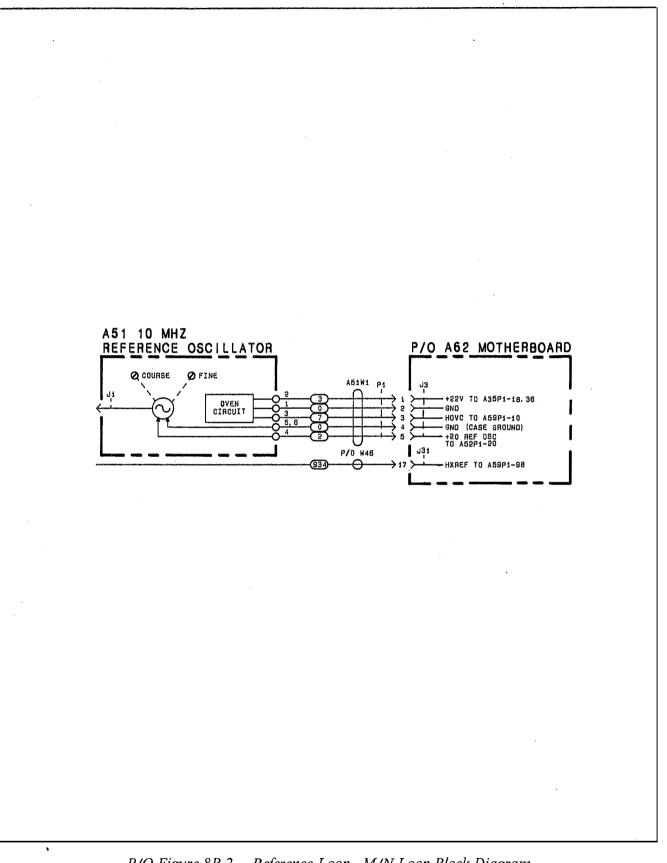

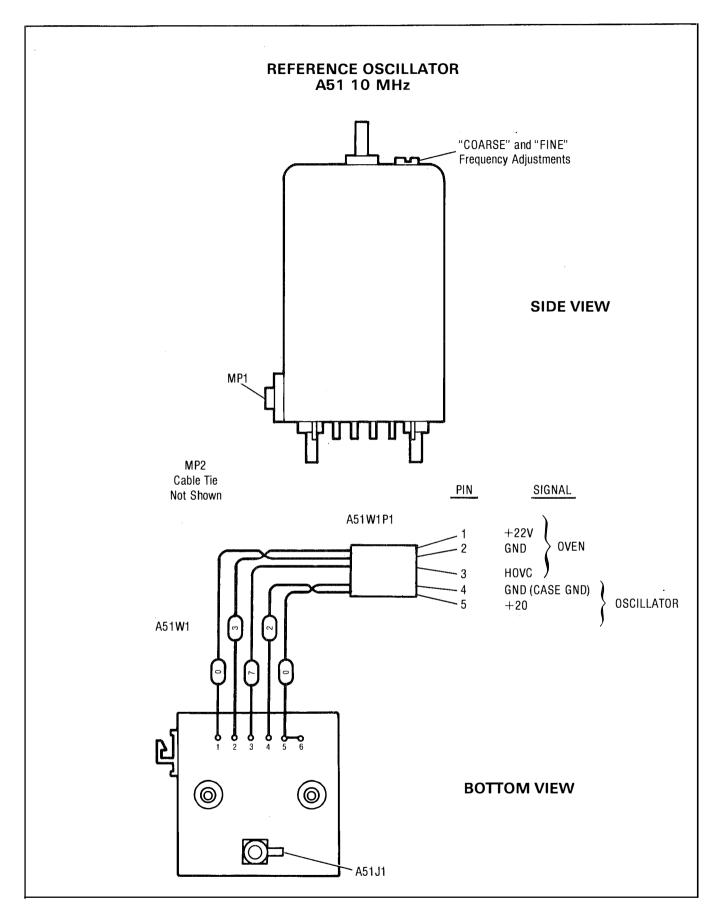

| A51<br>A52          | Reference Oscillator<br>Positive Regulator                           | 16<br>6  | •         |          |               |      |              |       |     |                     |    |

| A53                 | Negative Regulator                                                   | 7        |           |          |               |      |              |       |     | •                   |    |

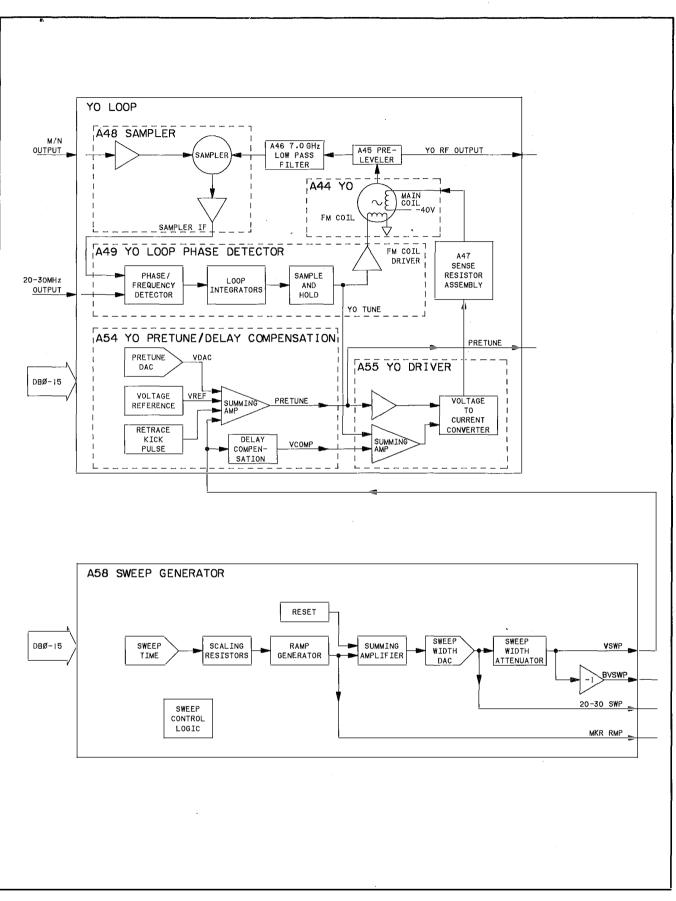

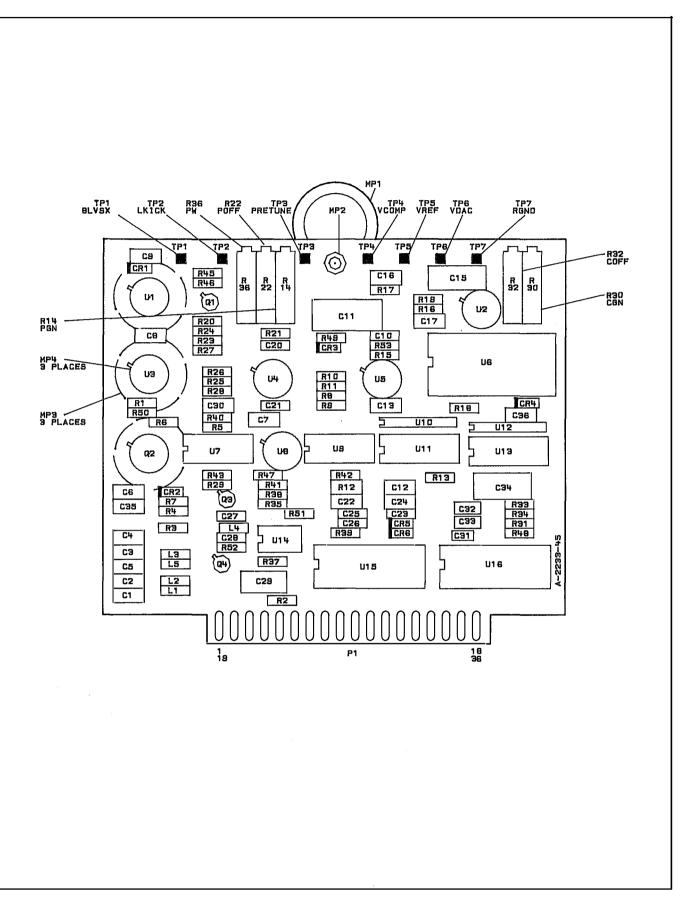

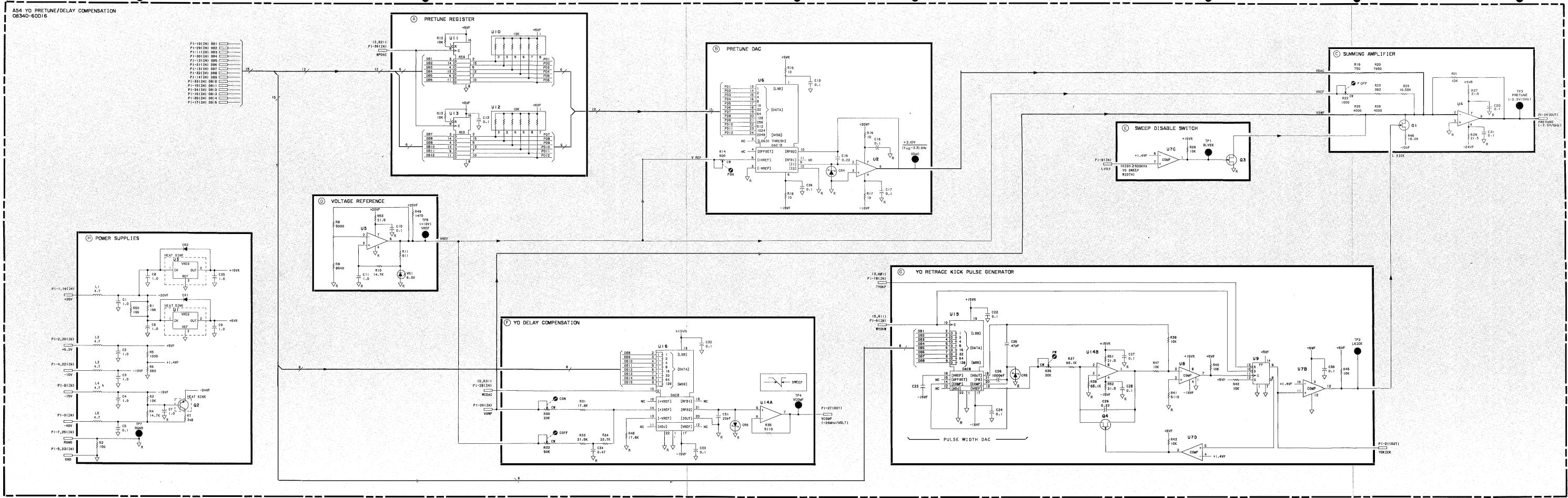

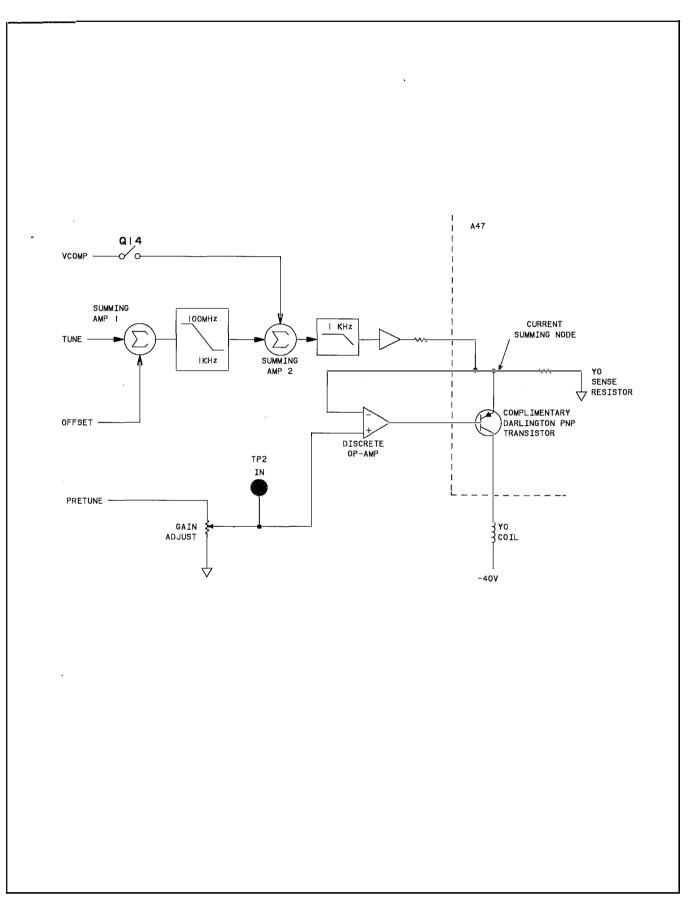

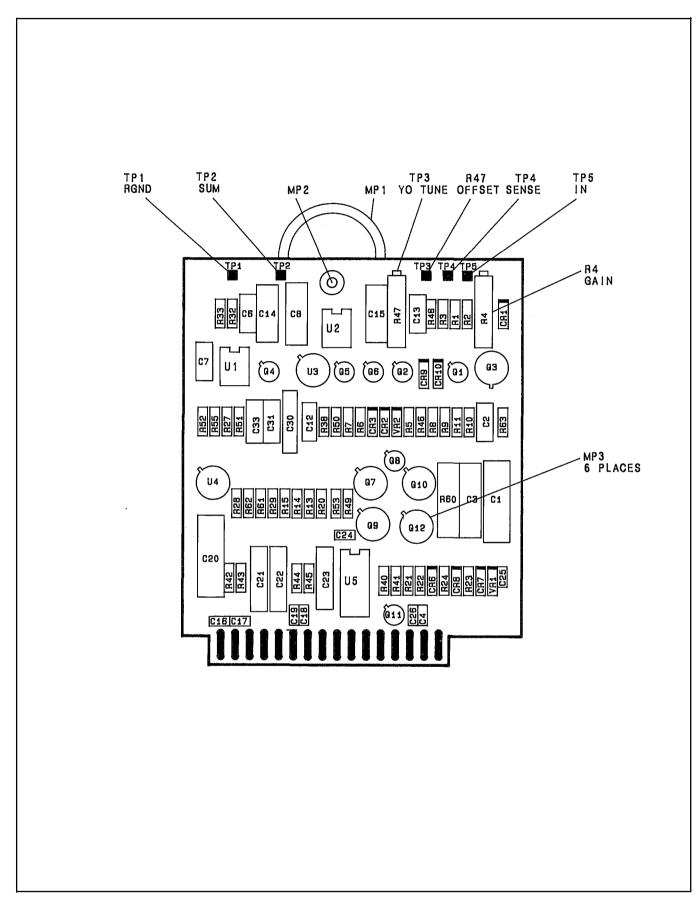

| A54<br>A55          | YO Pretune/Delay Compensation<br>YO Driver                           | 8<br>9   |           |          |               |      |              |       |     |                     |    |

| A56                 | – 15V Regulator                                                      | 10       |           |          |               |      |              | 1 - A | · . | •                   |    |

| A57<br>A58          | Marker/Bandcross<br>Sweep Generator                                  | 19<br>20 |           |          | •             |      | •            |       |     |                     |    |

| A59                 | Digital Interface                                                    | 21<br>22 |           |          |               |      | •            |       |     |                     |    |

| A60<br>A61          | Processor<br>Not Assigned                                            | 23       |           |          |               |      |              |       |     |                     |    |

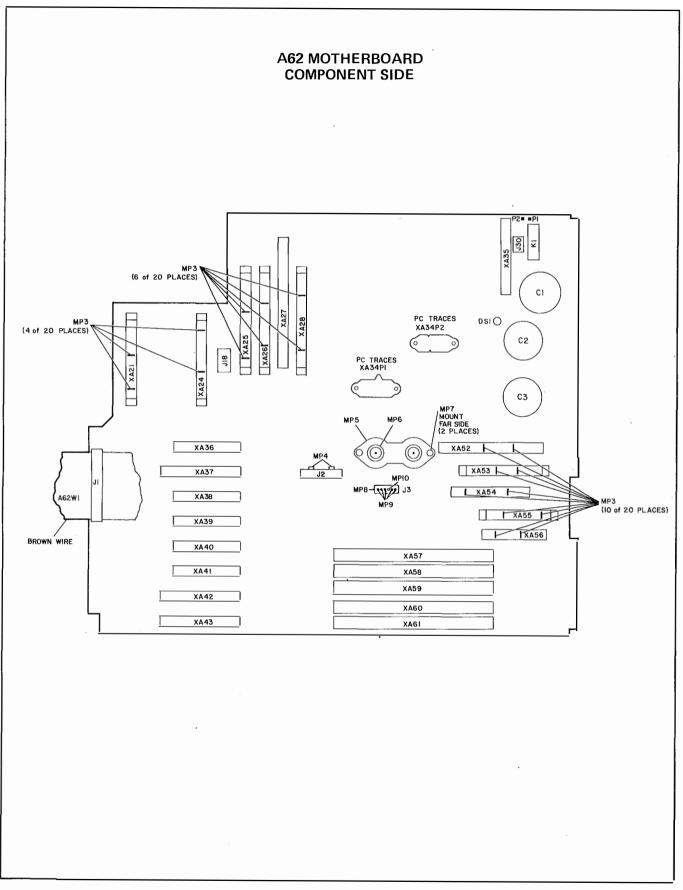

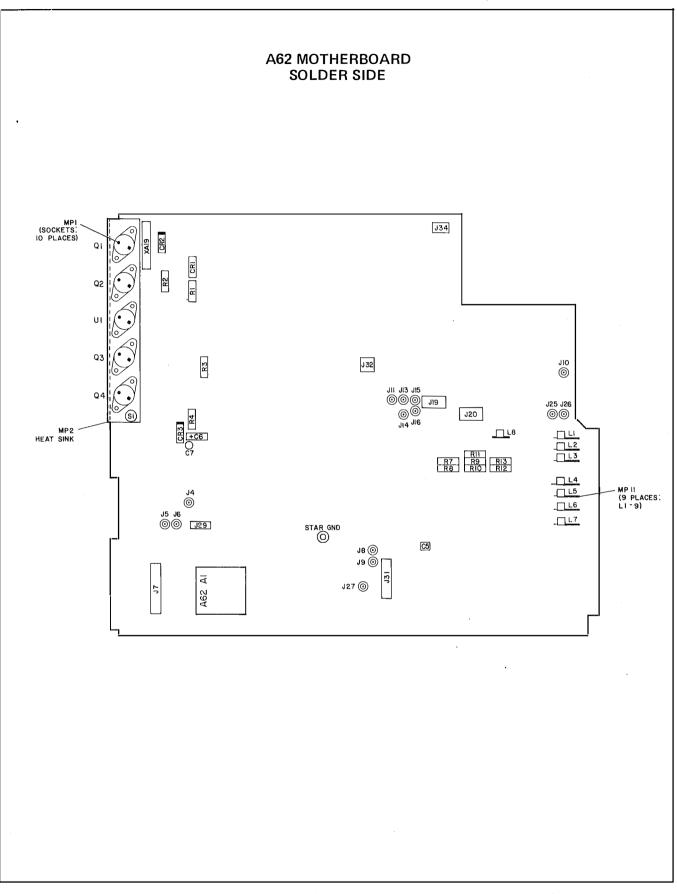

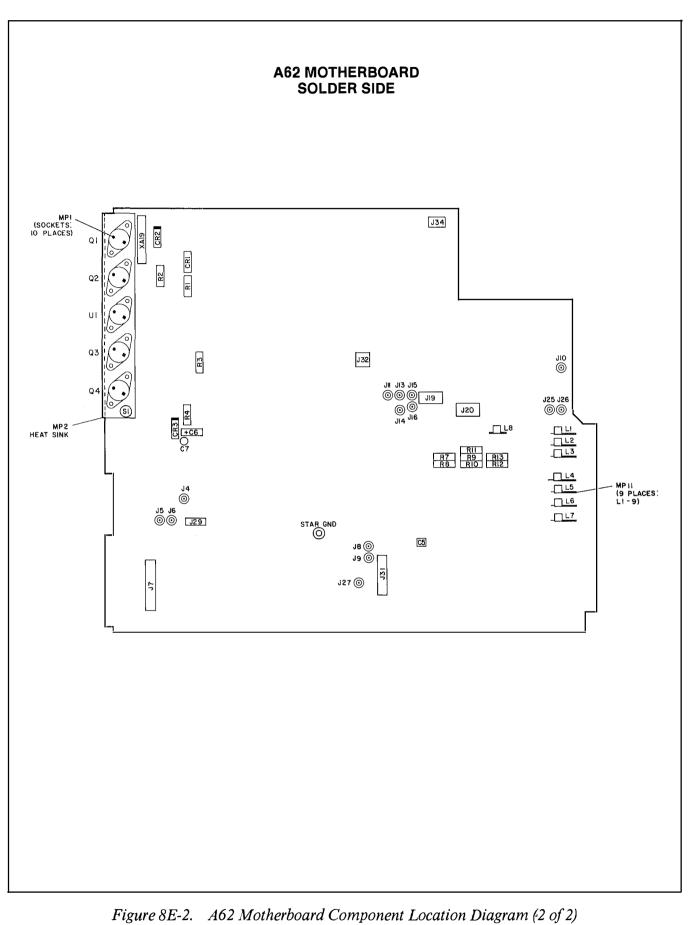

| A62<br>A63          | Motherboard<br>90 dB RF Attenuator                                   | 49<br>59 |           |          |               | ٠    |              |       |     |                     |    |

| AT1                 | Peripheral Mode Isolator                                             | 58       |           |          |               |      |              |       | •   |                     |    |

| AT2<br>B1           | 15 dB Attenuator<br>Fan Assembly                                     | 18<br>1  |           |          | ٠             |      |              |       |     |                     |    |

| A62C1-3             | Power Supply Filter Capacitors                                       | 3        |           |          |               |      |              |       |     | •                   |    |

| FL1<br>A62Q1-4      | AC Line Module<br>Power Supply Regulating Transistors                | 2<br>45  |           |          |               |      |              |       |     | :                   |    |

| A62S1               | Power Supply Thermal Switch                                          | 44       |           |          |               |      |              |       |     |                     |    |

| T1<br>A62U1         | Power Supply Transformer<br>Power Supply Regulator                   | 11<br>46 |           |          |               |      |              |       |     |                     |    |

|                     |                                                                      |          |           |          |               |      |              |       |     |                     |    |

Volume 3

Volume 4

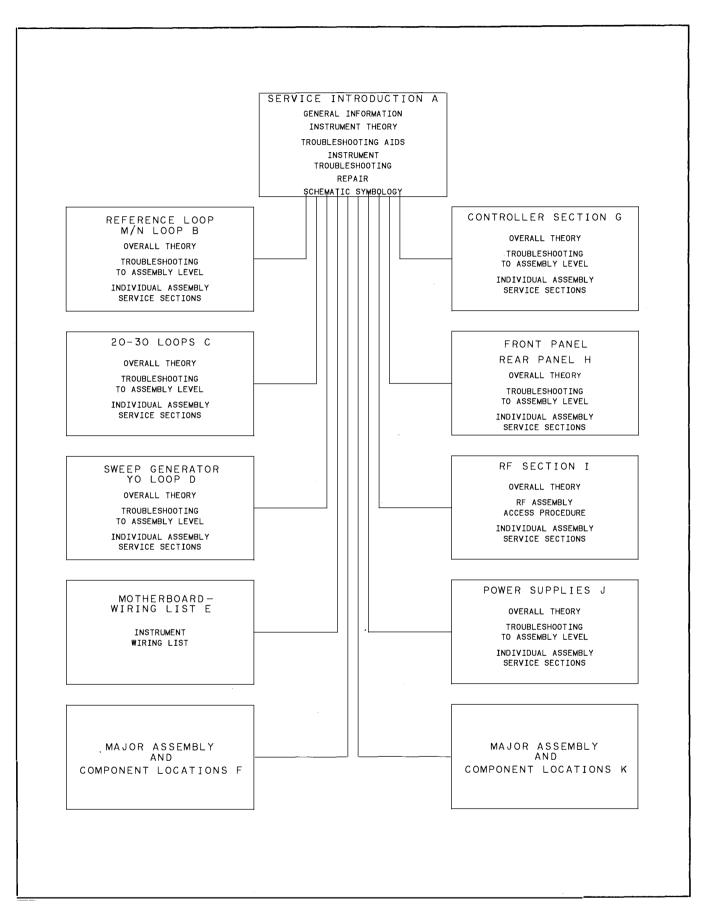

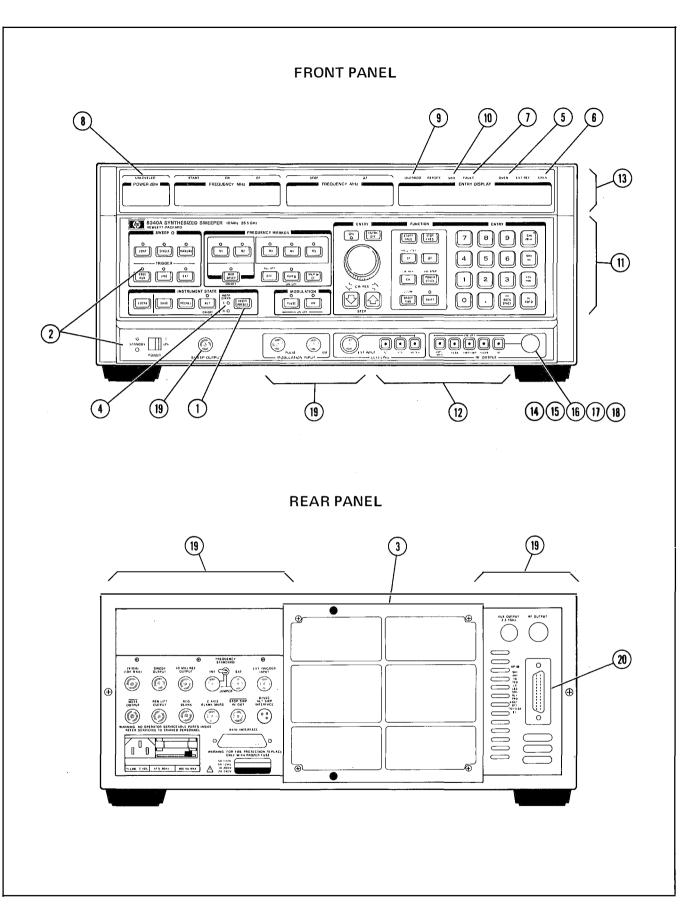

## SERVICE INTRODUCTION

This Service Introduction provides the troubleshooter with a structured procedure by which an instrument fault may be localized to the appropriate **functional group** (see below). The functional group provides the information required to troubleshoot to the component level. This section contains an "OVERALL THEORY OF OPERATION" and simplified block diagram. These are used in conjunction with the "OVERALL INSTRUMENT TROUBLESHOOT-ING," and "TROUBLESHOOTING AIDS" to determine the cause of the instrument failure. Information on safety and repair procedures is also included in this Service Introduction. Refer to the "SERVICE SECTION FORMAT" description, below.

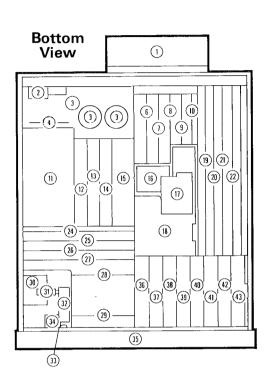

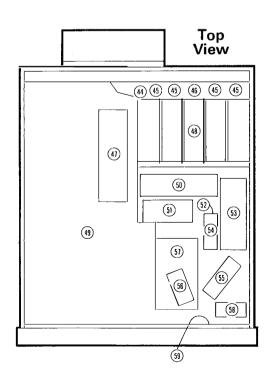

The HP 8340A Service Section is divided into eight sub-sections called functional groups. Four of these are listed on the front of each Service section tab along with a chart that shows which individual assemblies they contain and where these assemblies are located.

The tab for each of the eight functional groups provides an outline of the functional group's contents. Typically this includes an introduction, overall theory of operation, simplified block diagram, and a troubleshooting block diagram.

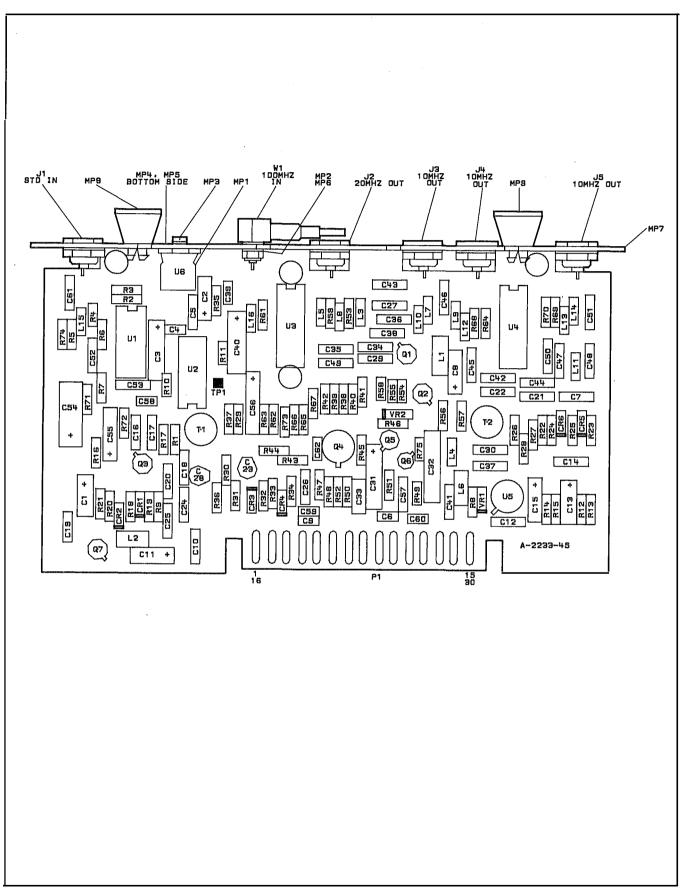

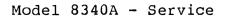

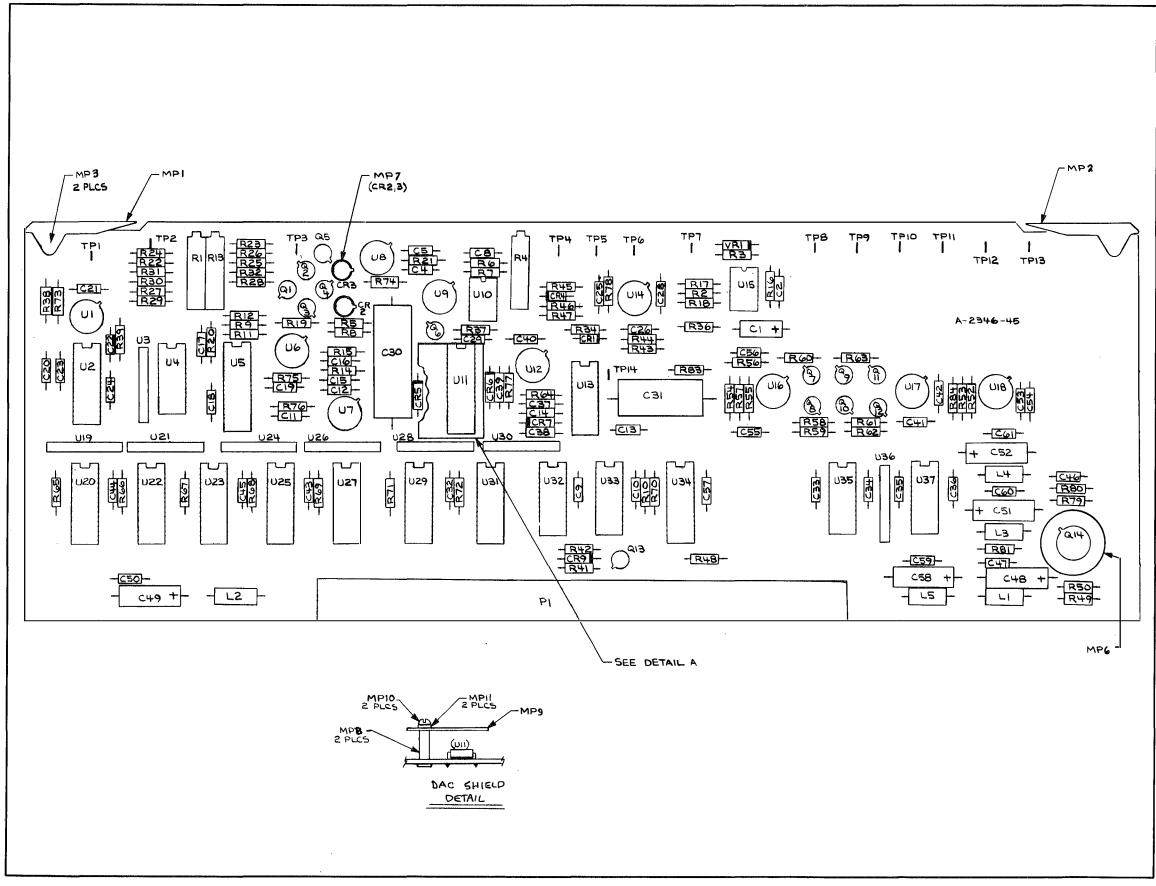

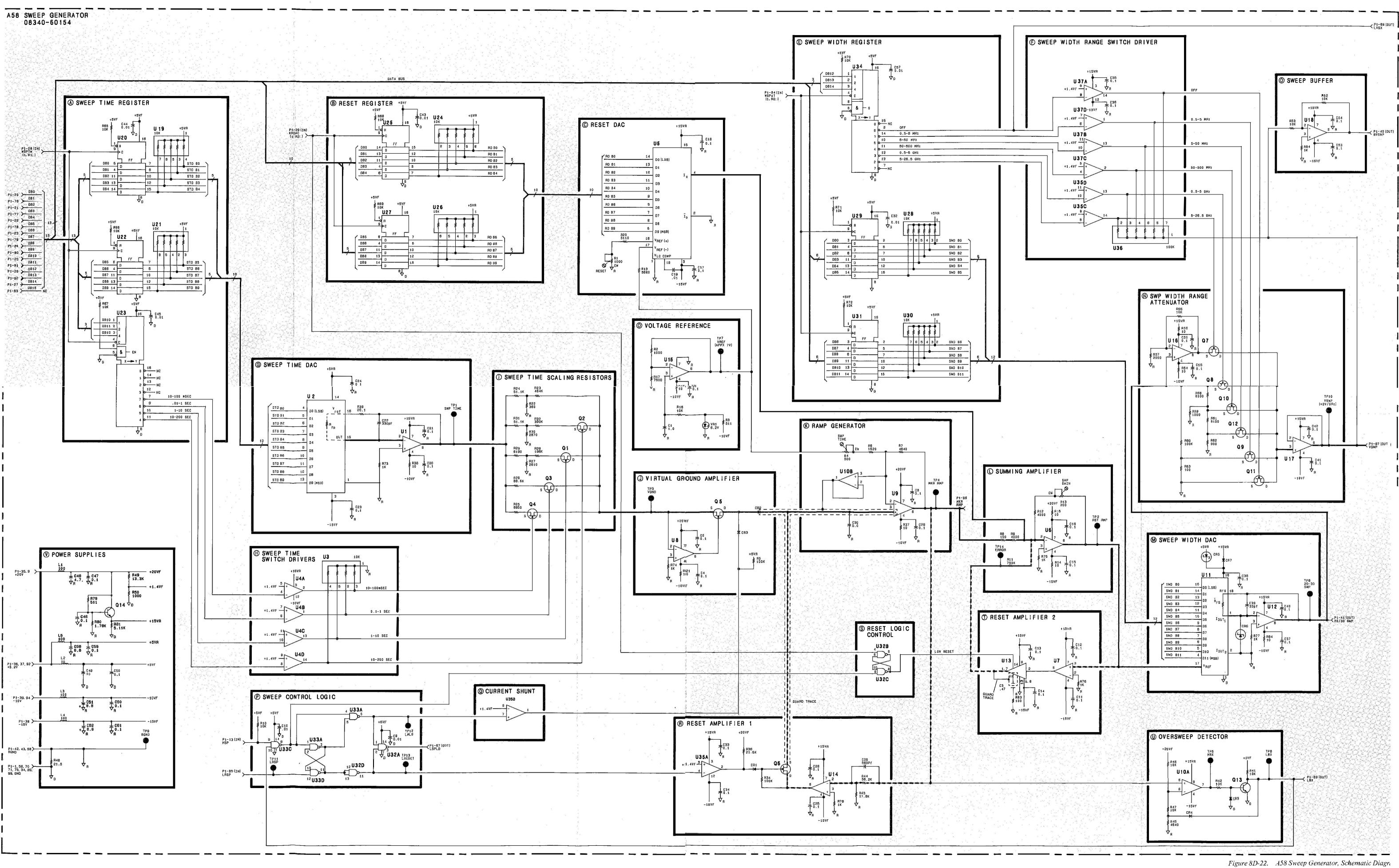

This is followed by a description of each assembly in the functional group. Each assembly description contains an overall theory of operation, simplified block diagram, component layout, pin I/O table and schematic diagram.

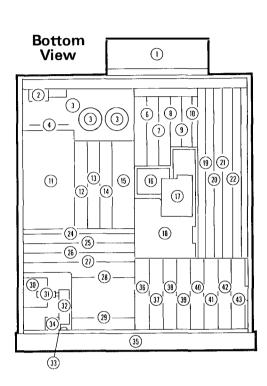

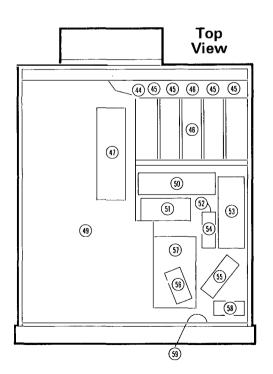

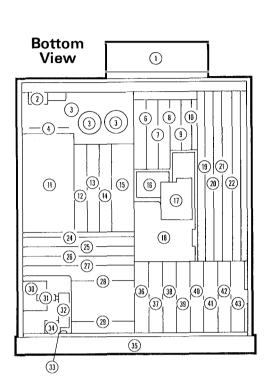

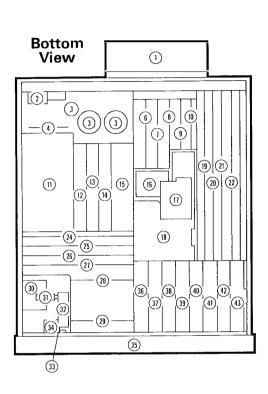

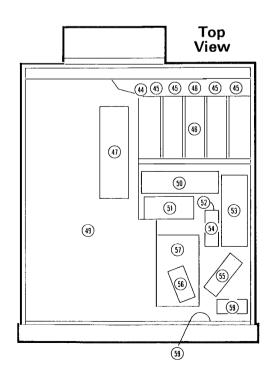

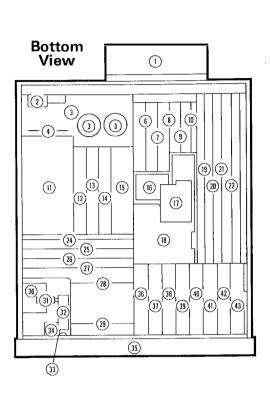

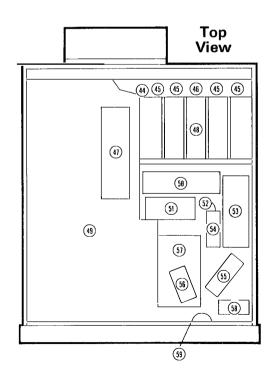

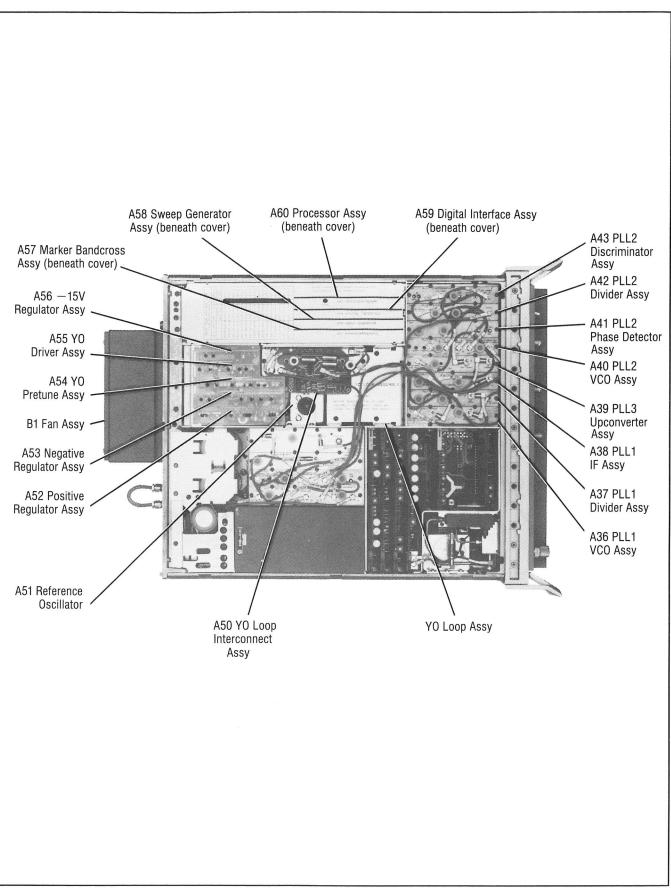

A Major Assembly and Component Locations diagram is provided at the end of each volume.

#### ATTENTION

In order to avoid unnecessary troubleshooting, verify the instruments internally stored calibration constants. If these constants have been incorrectly modified, the instrument may activate an error annunciator. To do this, first remove the hard copy of the calibration constants from the metal bracket inside the instrument on the left hand side panel (as viewed from the front). Compare these to the constants stored in memory per the instructions in the "CALIBRATION CONSTANTS" section, "Instrument User Access," step 1.

## SERVICE SECTION FORMAT

#### INTRODUCTION

The HP 8340A Service Section is structured to minimize the time it takes to troubleshoot a problem. The following text describes the format of the Service Section and provides important information concerning its use.

#### SECTION FORMAT

#### **General Information**

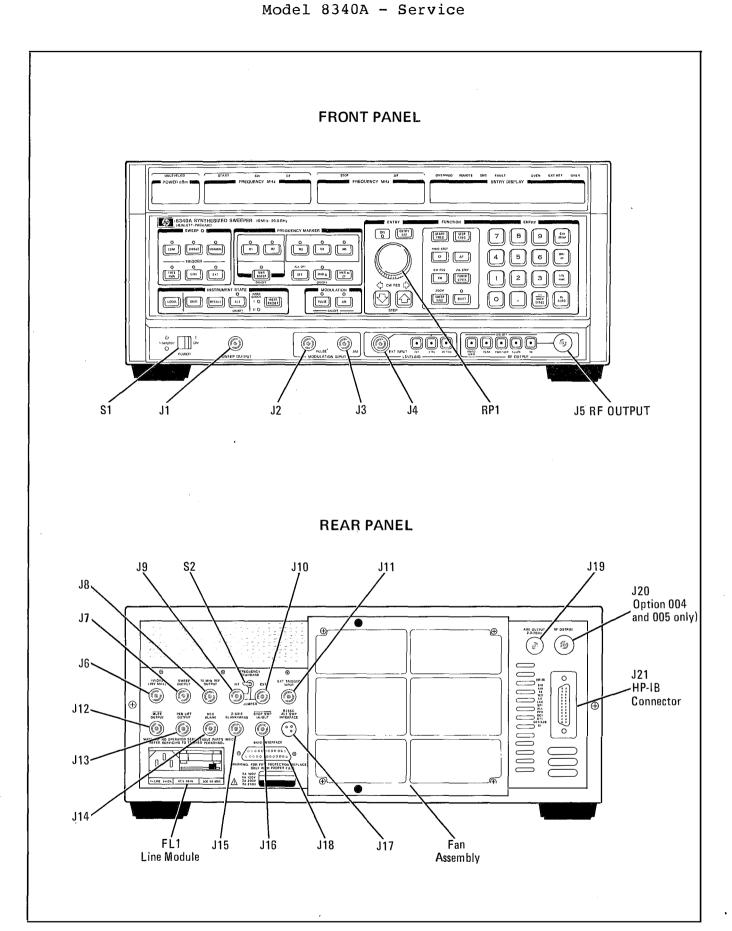

The beginning of Section VIII contains general information concerning safety, required tools, and the location of instrument interconnects and mnemonics.

#### **Overall Theory of Operation**

An Overall Instrument Theory of Operation is supplied that includes an overall block diagram of the instrument. A description of the instrument's stored Calibration Constants is also provided.

#### **Troubleshooting Aids**

This part of Section VIII contains descriptions of the troubleshooting aids that are built into the instrument. These aids are: the instrument Self-Test, Digital Signature Analysis (DSA), Direct I/O Addressing, and front panel Diagnostics.

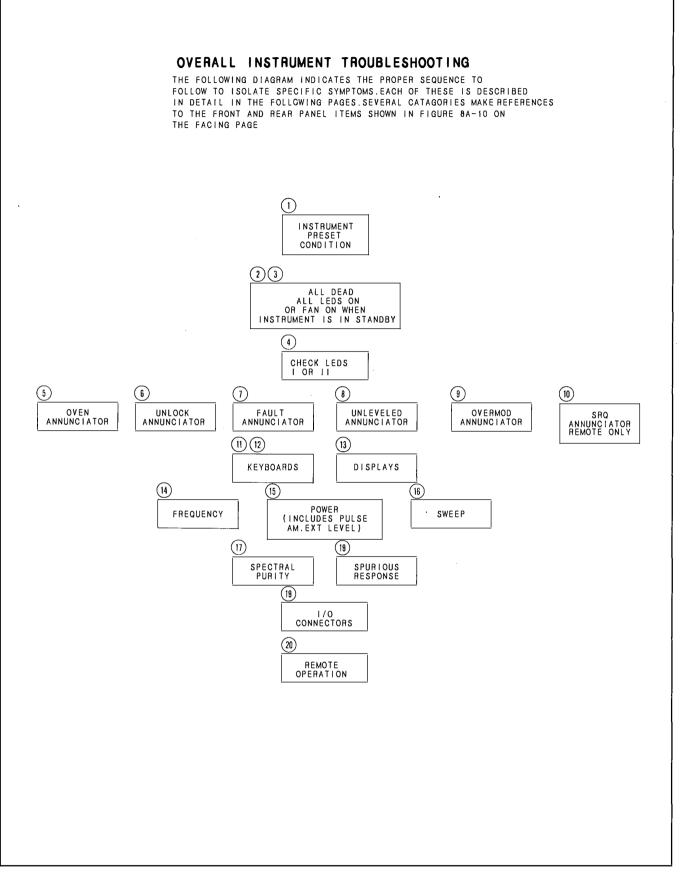

#### **Overall Instrument Troubleshooting**

This is the single most important part of the Service Section. This troubleshooting guide will allow the repair person to begin troubleshooting with a symptom and lead him or her to one of the eight major functional areas of the instrument (see below). In many cases this guide leads the troubleshooter directly to the faulty assembly.

#### Repair

This section contains warnings and cautions concerning the repair of the HP 8340A. It is extremely important that these precautions are implemented when repairing the instrument. A description of the microcircuit field exchange program and after-service safety checks is also included.

#### **Major Functional Group Service Sections**

A functional group is a group of assemblies that work in conjunction with one another to perform a certain task. There are eight such groups in the HP 8340A. These are:

- Reference Loop M/N Loop

- 20-30 Loops

- Sweep Generator YO Loop

- Motherboard Wiring List

- Controller Section

- Front Panel Rear Panel

- RF Section (Power Level Control)

- Power Supplies Fan

These sections are further divided into overall troubleshooting guides, one for each of the above functional groups. Each of these guides contains the theory of operation and block diagrams for the functional group as a whole. This is followed by a service guide for each assembly that makes up that functional group. These assembly level service guides contain; theory of operation, troubleshooting information, block diagrams, a component location diagram, a pin I/O table, and a schematic diagram.

•

8-5/8-6

## WARNING

When connected to ac mains, there are voltages at points inside the instrument that can cause personal injury or even death. Any servicing of this instrument with protective covers removed should be performed only by trained personnel who are aware of the hazard involved.

If the A19 POWER-ON SAFETY INDICATOR LED is on, there are voltages present inside the instrument (the A62 Motherboard, the A35 and A19 Rectifier Assemblies, line filter module/transformer wiring, etc.) that can cause injury or even death.

Whenever the instrument is connected to ac mains, the A19 and A35 rectifiers, as well as the A35 +22V REGULATOR, are fully operational. All filter capacitors are charged to full potential. This is true regardless of the position of the POWER switch. Only the A52, A53, and A56 regulators are turned off when the POWER switch is set to STANDBY.

Capacitors inside the instrument may still be charged even if the instrument has been disconnected from ac mains. The A19 POWER-ON SAFETY INDICATOR indicates that the filter capacitors on the A19 assembly are sufficiently charged to constitute a shock hazard. Wait until this LED is out before touching any internal components. The filter capacitors on the A35 RECTIFIER assembly bleed-off faster than the A19 capacitors. Therefore, by the time the A19 POWER-ON SAFETY INDICATOR LED is dark, (and the A35 assembly is connected to all of its normal loads) the A35 capacitors have had time to discharge.

Any interruption of the protective (grounding) conductor (inside or outside the instrument) or disconnecting the protective earth terminal will cause a potential shock hazard that could result in personal injury or even death. (Grounding one conductor of a two conductor outlet is not sufficient protection). Whenever it is likely that this protection has been impaired, the instrument must be made inoperative and be secured against any unintended operation.

If this instrument is to be energized via an autotransformer, make sure the common terminal is connected to the earth terminal of ac mains.

For continued protection against fire hazards, replace the LINE fuse only with 250V normal blow fuses with the proper current rating. Do not use repaired fuses or short circuited fuseholders.

## CAUTION

Never short a capacitor with a screwdriver or similar direct short. Instead, either wait for the capacitor to bleed off via normal instrument loads or, if this is not convenient, provide a discharge path by applying a 0.5 watt, 100 ohm resistor (via shielded clip leads) across the capacitor terminals.

## GENERAL INFORMATION

#### **TOOLS REQUIRED**

As mentioned above, a soldering station equipped with a grounded tip as well as a low static solder removal tool are required. The Ungar HOT VAC or equivalent is recommended for removing motherboard connectors. Other than these items, no special equipment is needed that isn't provided in the Service Kit (HP Part Number 08340-60134). Table 8A-1 is a list of the tools included in this kit:

| ltem               | Description                                                                                                                                | HP Part<br>Number                                                                                     |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Adapters           | APC-3.5 Female to Female<br>APC-3.5 Female to Type N Male                                                                                  | 5061-5311<br>1250-1744                                                                                |

| Adapter Tee        | SMB Male-Male-Male                                                                                                                         | 1250-0670                                                                                             |

| PC Board Extenders | 24-pin<br>30-pin<br>36-pin<br>44-pin<br>48-pin<br>62-pin<br>110-pin                                                                        | 08340-60095<br>08505-60041<br>08505-60042<br>08350-60031<br>08340-60050<br>08340-60096<br>08340-60033 |

| IC Test Clip       | 16-pin<br>20-pin                                                                                                                           | 1400-0734<br>1400-0979                                                                                |

| Adjustment Tool    | Fits adjustment slot on components                                                                                                         | 8830-0024                                                                                             |

| Service Cables     | <ul> <li>BNC (Male) to SMB (Female) (2 required)</li> <li>61 mm (2 ft), 0.85 in., semi-rigid, SMA Male to SMA Male (2 required)</li> </ul> | 85680-60093<br>08340-20124                                                                            |

|                    | 30 mm (12 in) SMB (Female) to SMB (Female)                                                                                                 | 5061-1022                                                                                             |

| Nut Driver         | 9/16 inch, to replace front panel BNC nuts                                                                                                 | 08340-20099                                                                                           |

| Wrench             | 5/16-inch slotted box/open end                                                                                                             | 08555-20097                                                                                           |

Table 8A-1. Tools Supplied in Service Kit

| Table 8A-2. | Equipment Not Supplied in Service Kit |

|-------------|---------------------------------------|

|-------------|---------------------------------------|

| Item                | Description                                           | HP Part<br>Number |

|---------------------|-------------------------------------------------------|-------------------|

| RMA Solder          | Rosin Mildly Activated                                | 8090-0587         |

| EDSYN<br>SILVERSTAT | Low static solder removal tool                        | 8690-0227         |

| Replacement Tip     | For low-static solder removal tool                    | 8690-0253         |

| Wrist Strap         | Anti-static wrist strap, 4 ft cord and alligator clip | 9300-0791         |

#### INTERCONNECT CABLES AND MNEMONICS

.

All interconnect cables and their associated connectors are listed in Table 8E-1, located within the A62 Motherboard Functional Group.

Table 8E-1 alphabetically lists and defines all HP 8340A signal mnemonics, references the pointto-point distribution of each signal to and from the PC board sockets and the cable connectors on the A62 Motherboard assembly, and identifies the signal source. This table is located in the A62 Motherboard Functional Group.

## HP 8340A OVERALL INSTRUMENT THEORY

#### INTRODUCTION

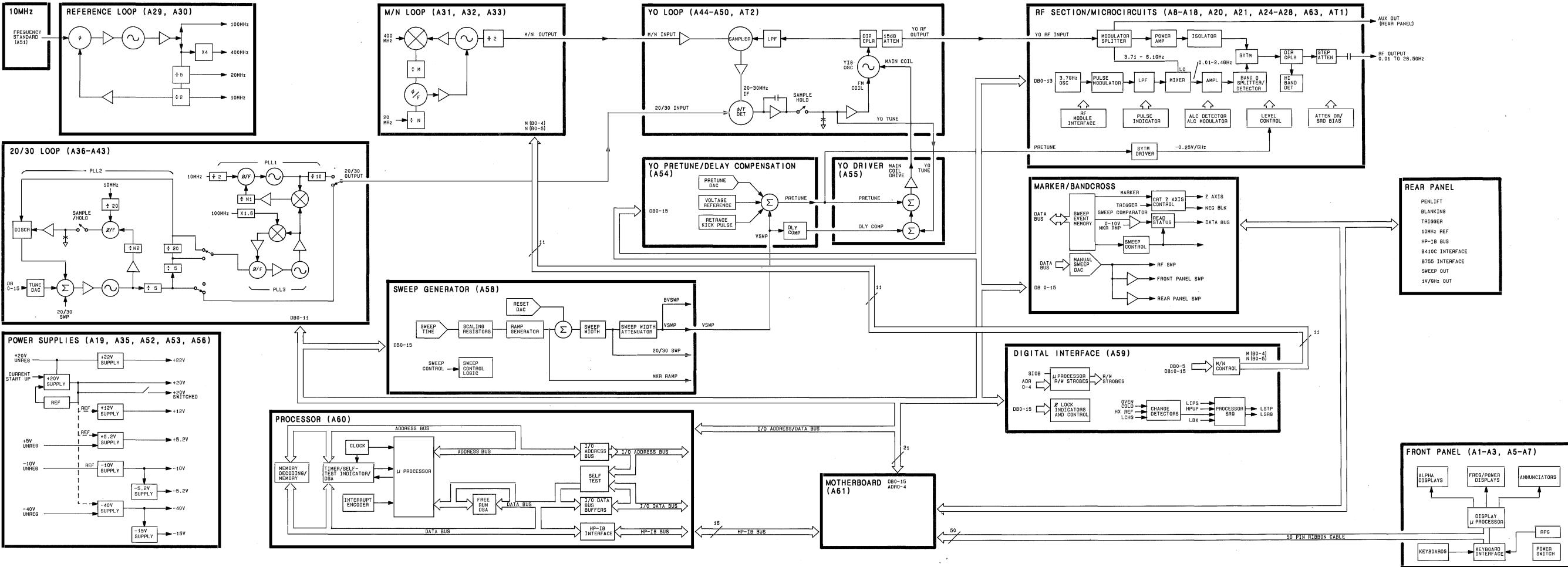

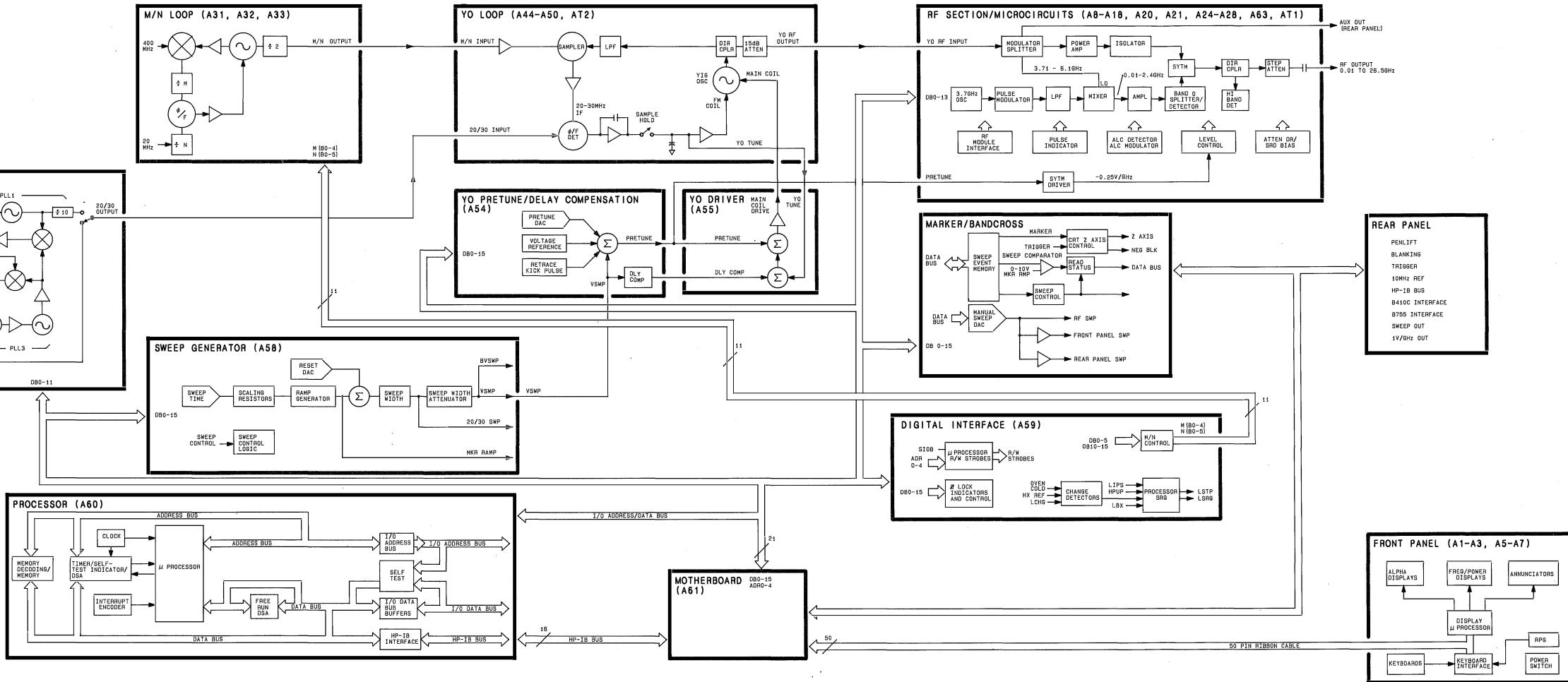

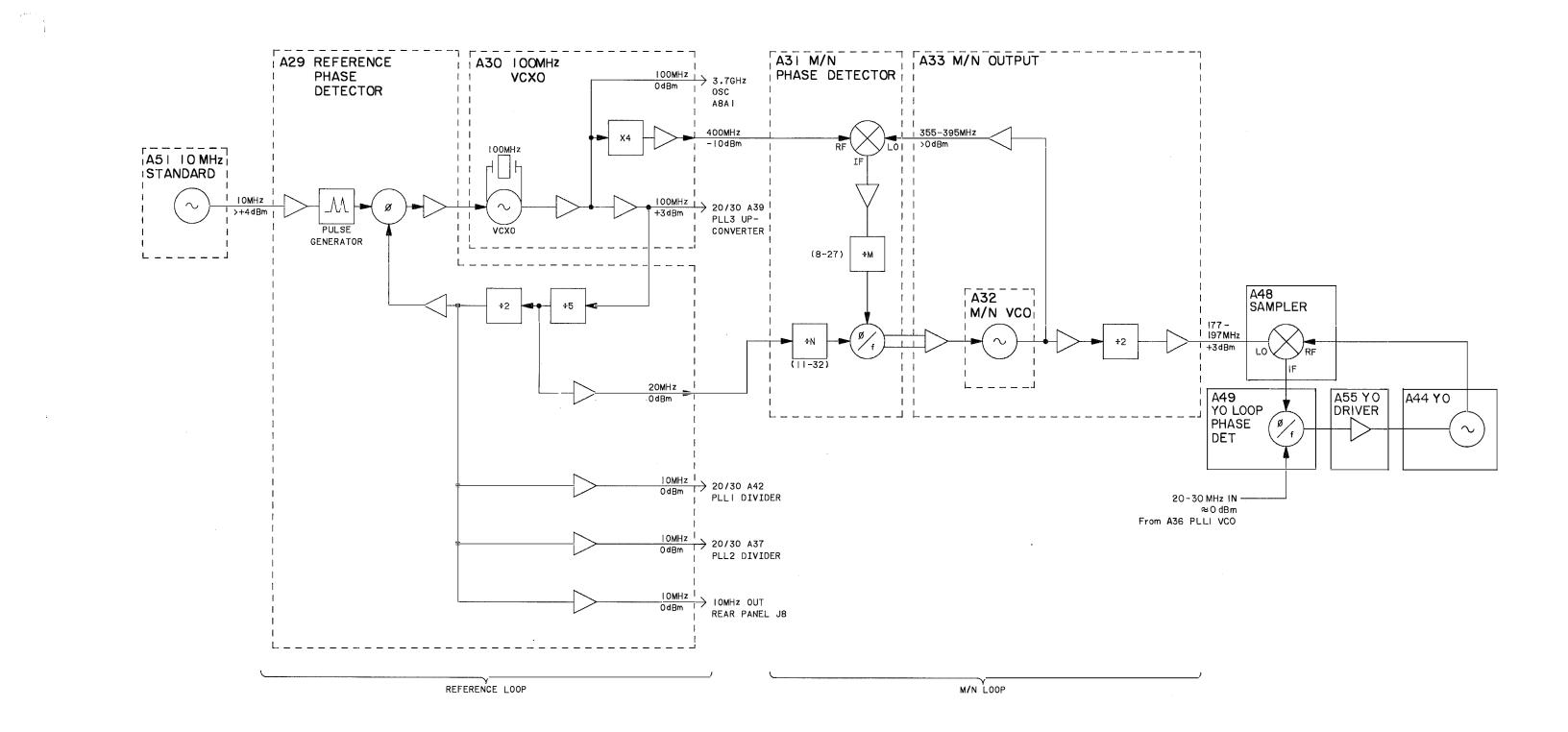

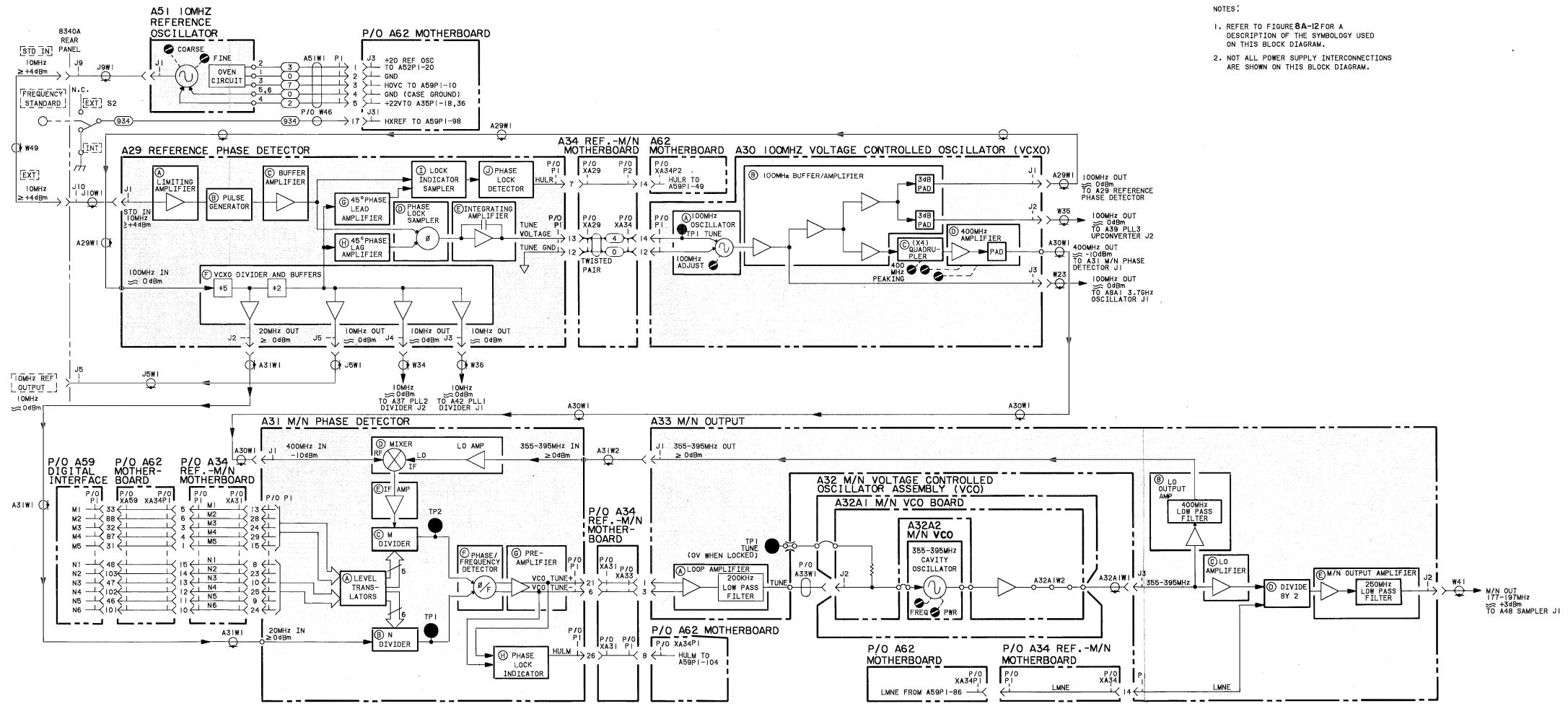

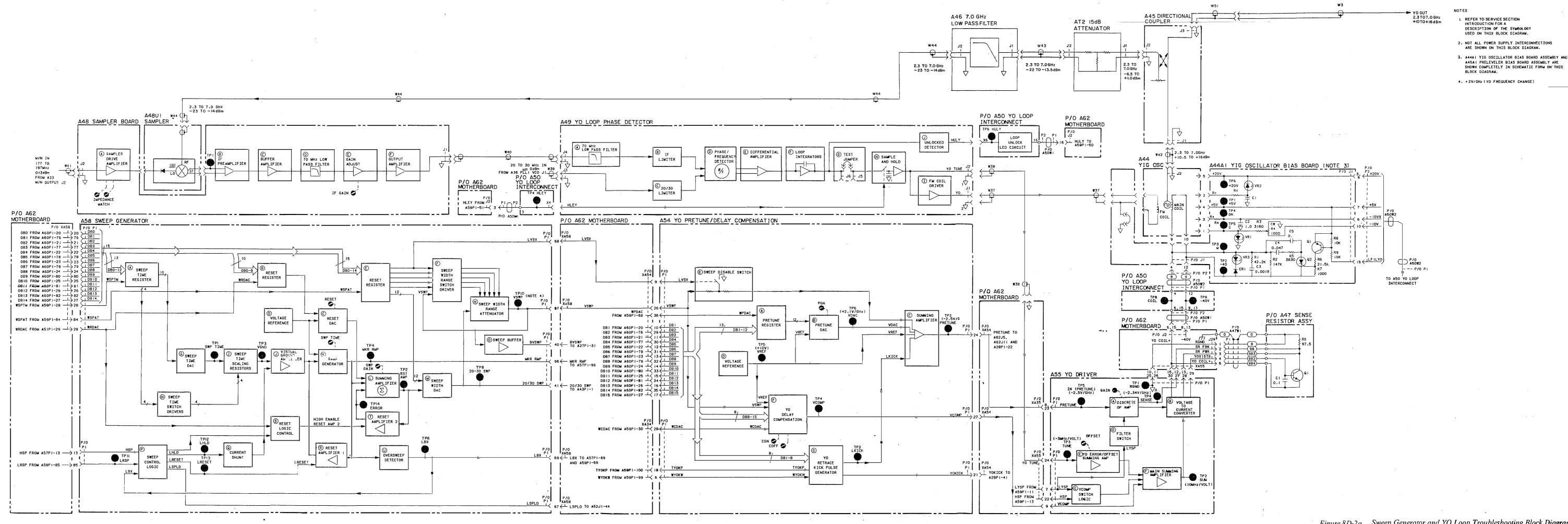

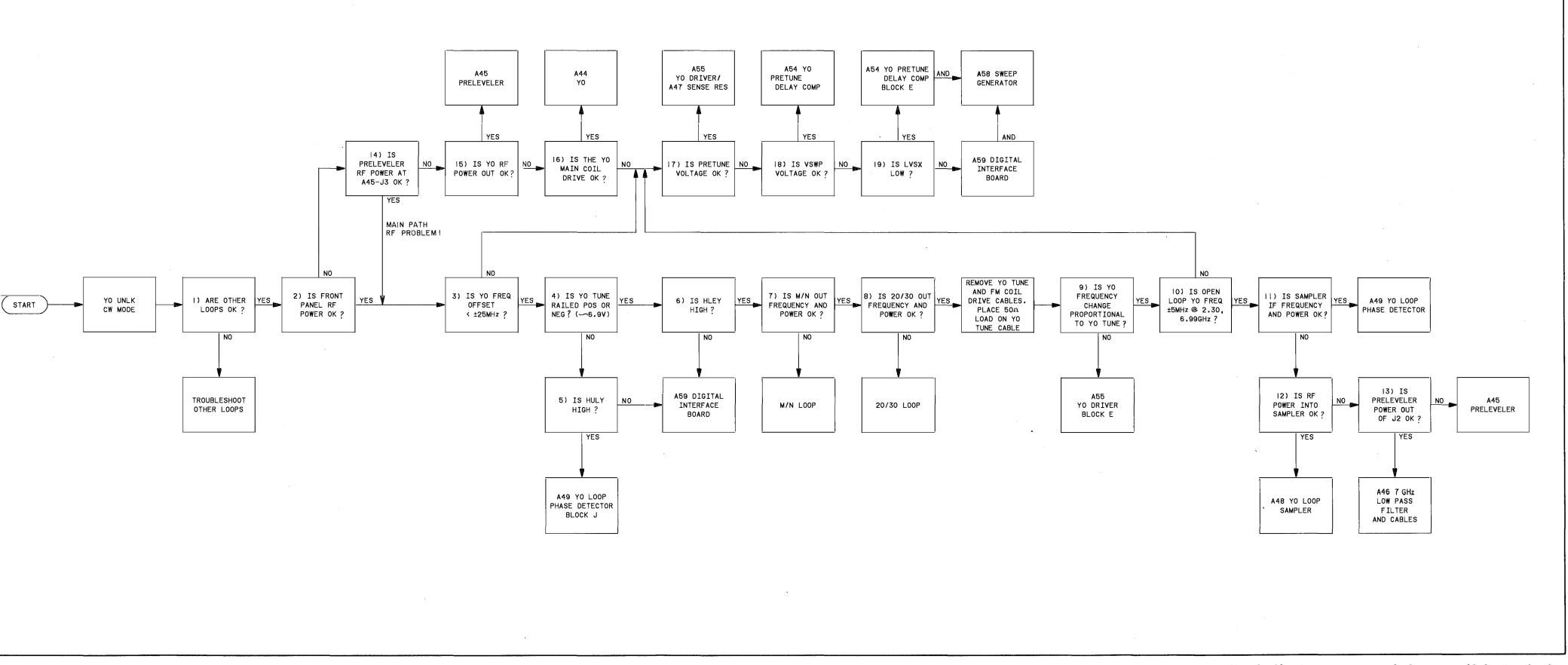

Refer to Figure 8A-2, HP 8340A Block Diagram.

The HP Model 8340A is a synthesized sweeper that covers the frequency range from 10 MHz to 26.5 GHz in five bands. These bands are:

- Band 0 (10 MHz to 2.3 GHz)

- Band 1 (2.3 to 7.0 GHz)

- Band 2 (7.0 to 13.5 GHz)

- Band 3 (13.5 to 20.0 GHz)

- Band 4 (20.0 to 26.5 GHz)

Internal to the HP 8340A are 7 phase-lock loops, 16 high frequency microcircuits, and a 16 bit microprocessor. these provide the capability of broadband sweeps and the frequency accuracy of a high-performance synthesizer.

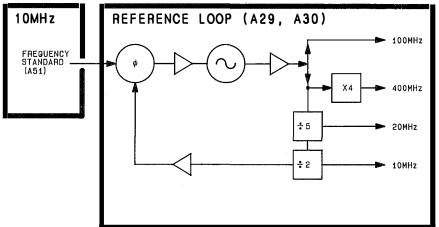

#### **REFERENCE LOOPS**

The HP 8340A's frequency accuracy and stability are tied to either the 10 MHz internal frequency standard or an external 10 MHz source. The Reference Loop uses this 10 MHz source to generate all of the translation and reference signals that are used by other phase-lock loops inside the instrument. These signals are:

- 400 MHz and 20 MHz signals used in the M/N Loop to produce the M/N output frequency.

- 10 MHz and 100 MHz signals used as reference signals in the 20-30 Loops.

- A separate, lower power 100 MHz output sent to the RF Section for phase locking the 3.7 GHz Oscillator to the 10 MHz Reference.

#### M/N LOOP

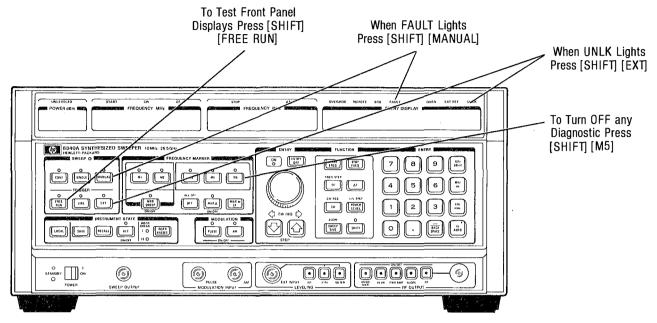

The M/N Loop produces an output between 177-197 MHz. This M/N output drives a Sampler in the YO Loop. The variables "M" and "N" are integers generated by the processor and control the output frequency of the M/N Loop. The output from the Sampler in the YO Loop must always be between 20-30 MHz for the instrument to phase-lock. With the YO at a specific frequency between 2.3 and 7.0 GHz there will be an M/N output frequency between 177 and 197 MHz. When a harmonic of this frequency is mixed with the YO frequency in the Sampler, an IF output between 20-30 MHz will result. the Sampler output is then compared to the 20-30 Loop output by the YO Loop Phase/Frequency detector in the YO Loop.

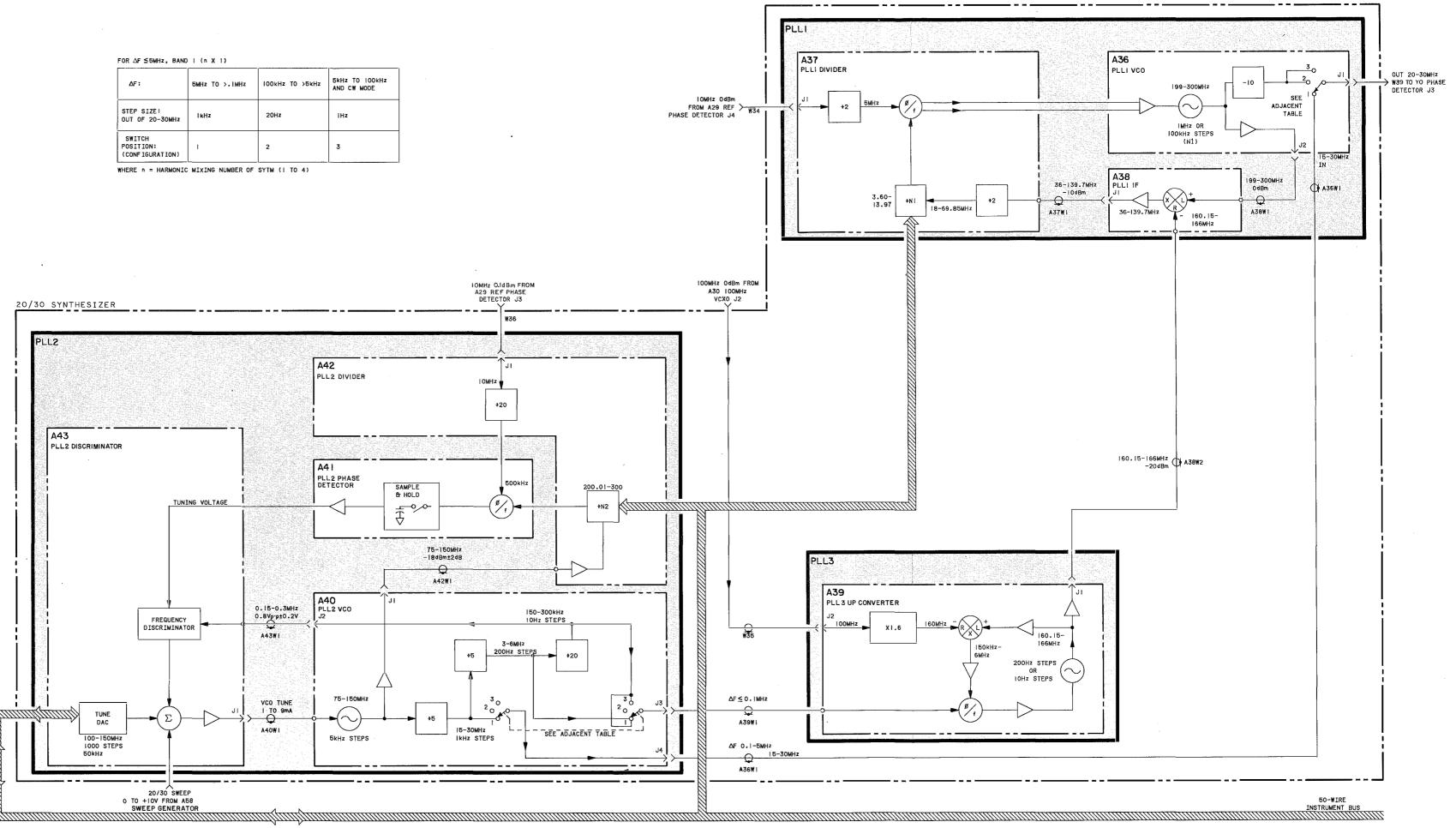

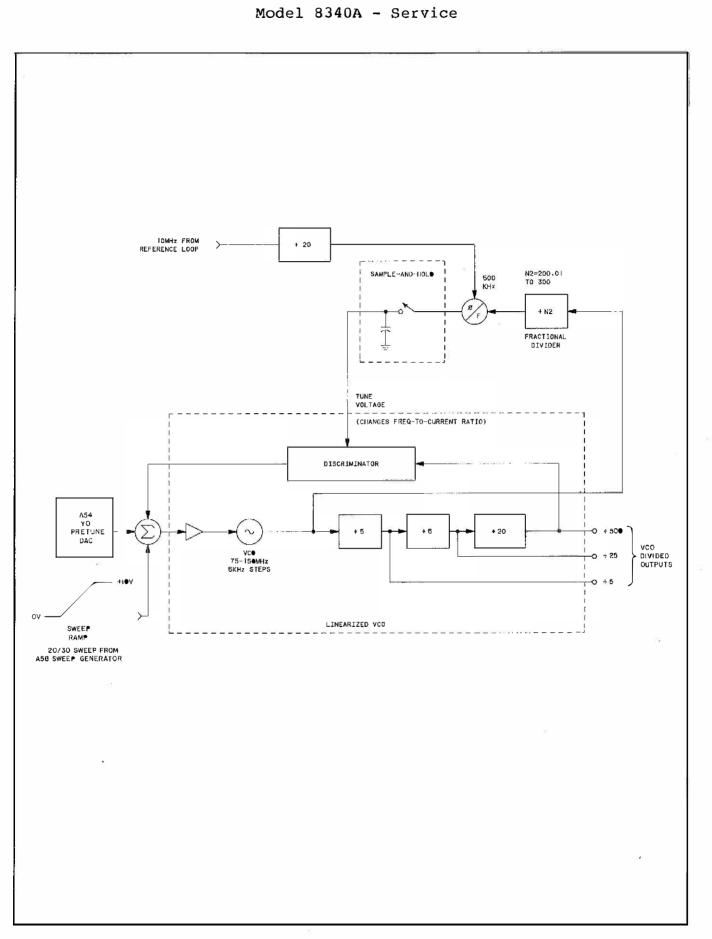

#### 20-30 LOOPS

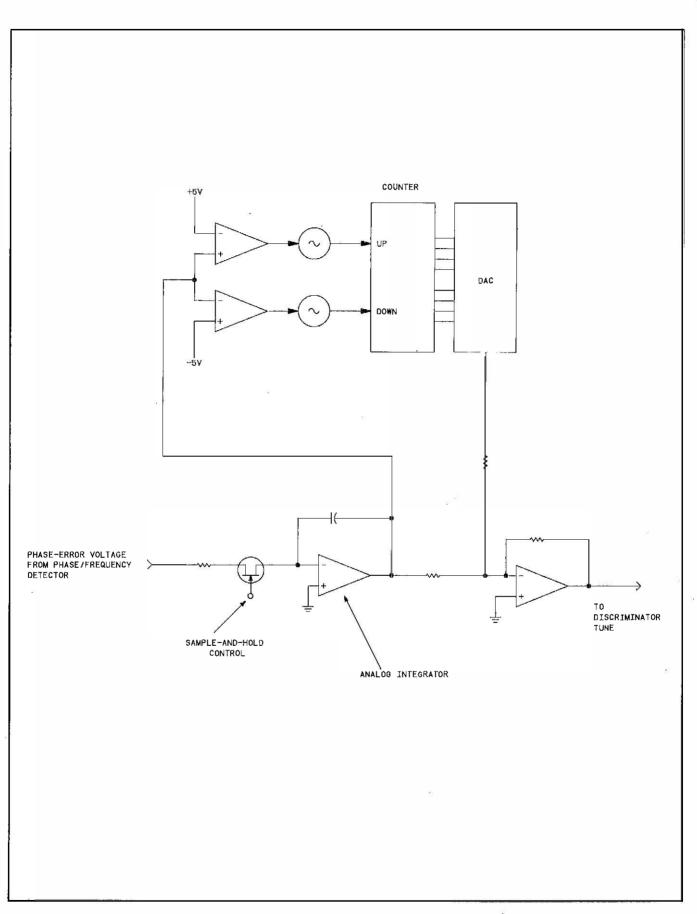

The 20-30 Loops contain 3 phase-locked loops that are used in conjunction with one another to provide the HP 8340A YO Loop with 1 Hz CW resolution, and with analog sweep widths from 100 Hz to 5 MHz. For sweep widths  $\leq$ 5 MHz the YO Loop remains phase-locked during the sweep, and the 20-30 Loop is swept the desired amount. For sweep widths  $\geq$ 5 MHz, all phase-lock loops lock at the beginning of sweep, the 20-30 Loop remains fixed, and the YO is swept. This is called Lock and Roll and will be discussed later.

The 20-30 Loop generates an output between 20-30 MHz in CW mode and 15-30 MHz when the 20-30 Loop is swept. This loop has an output resolution of 1 Hz. Comparing and locking the down-converted YO frequency to the 20-30 output produces a 1 Hz resolution in the YO frequency.

#### YO LOOP

The YO Loop contains the YIG Oscillator (YO) that is the tunable local oscillator source for all frequency bands. When the HP 8340A is set to a specific CW frequency, the processor sets the frequency of the M/N and 20-30 Loops accordingly. It also sets the YO pretune voltage which tunes the YO to the approximate frequency.

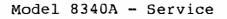

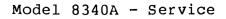

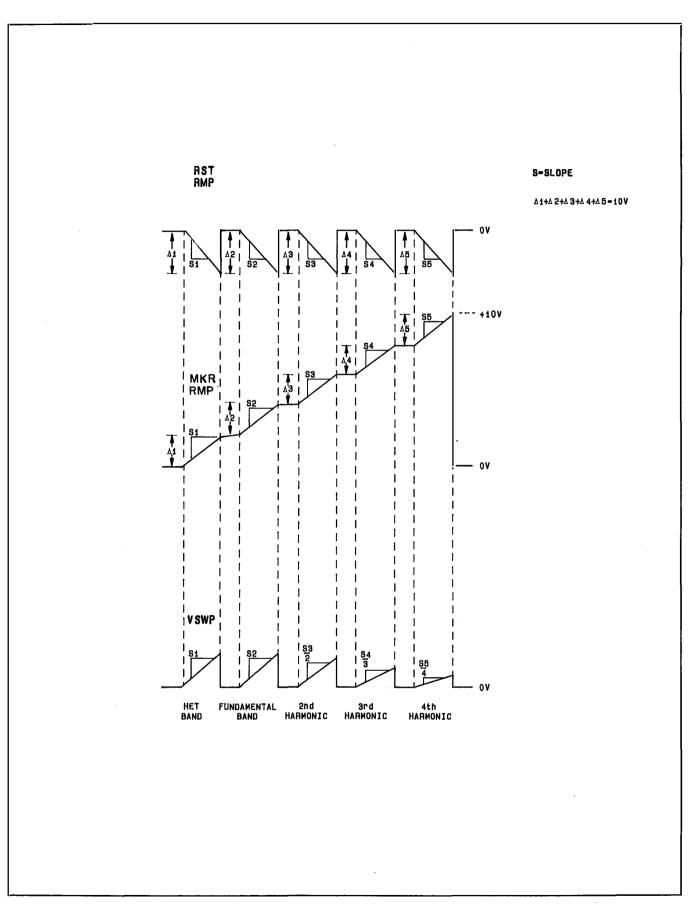

The output of the YO is fed through the directional coupler to the RF Section. The directional coupler splits off part of the YO signal which goes to the Sampler. The M/N output frequency and its harmonics are mixed with the YO frequency in the Sampler to produce an IF signal between 20-30 MHz. The 20-30 MHz IF from the Sampler is compared to the 20-30 Loop output in the Phase/Frequency Detector. The error-induced voltage from the Phase/Frequency Detector is fed through a sample/hold and is summed with the pretune voltage that drives the YO tuning coils. The YO Frequency changes until the output voltage from the Phase/Frequency Detector goes to zero and phase-lock is achieved. For sweep widths greater than 5 MHz, the YO is phase-locked at the start of the sweep. The sample/hold is then set to hold, breaking the loop, and allowing the YO to sweep. The Sweep Generator initiates a Voltage-Sweep (VSWP) ramp that is summed with the YO pretune voltage. This voltage causes the YO to sweeps, the STOP frequency. This action is referred to as Lock and Roll. During multi-band sweeps, the YO will again phase-lock at the start of each band before continuing on with the sweep, thus ensuring frequency accuracy across the full range of the HP 8340A.

#### CONTROLLER SECTION

The Controller Section performs all of the data transfer and coordinates the control signals that operate the HP 8340A. It contains a 16 bit microprocessor, a total of  $34K \times 16$  ROM and  $8K \times 16$  RAM. This section also contains interface circuitry for communicating with the rest of the instrument.

Digital information is exchanged between the microprocessor and other sections of the instrument on a bidirectional bus. In the power-on condition or at Instrument Preset, the controller runs through an instrument self-test. The microprocessor will also set the front panel controls to preset conditions if Instrument Preset was pressed.

The rear panel interface signals, such as the HP-IB bus, SWEEP OUTPUT, Z-AXIS, and others are also routed through or generated in the Controller functional group. The sweep control signal from the controller stops and starts the Sweep Generator. As previously mentioned, during bandcrossings, the sweep must be stopped to phased lock the YO before the sweep can continue. The controller monitors sweep events such as bandcrossings, end of sweep, and markers. It then executes specific instructions according to each type of sweep event.

#### FRONT PANEL

The front panel contains both the displays and the keyboard as well as some interface connectors. The display has a dedicated microprocessor that keeps the display refreshed and updated. When the instrument processor places display data into the display interface latch, it signals the display processor that some information is ready. The display processor immediately takes the data from the latch and stores it in internal memory. The data will be handled when the display processor has time. The keyboard communicates directly with the instrument processor. When a key is pressed, the instrument processor will either execute that key (if it is a single key operation), or wait for completion of the key sequence. Different key sequences not only allow the operator to set up the HP 8340A for normal operation but also allow access to internal registers, latches, D to A converters, and calibration constants for troubleshooting.

#### **RF SECTION**

The RF Section contains the microcircuits and control circuits that produce the 10 MHz to 26.5 GHz RF OUTPUT from the 2.3 to 7.0 GHz YO loop output.

RF output from the directional coupler in the YO loop is fed to the Modulator/Splitter (Mod/Splitter) in the RF Section. Band 0 (10 MHz to 2.3 GHz) is the heterodyne band and is produced by mixing a swept LO Drive from the Mod/Splitter with the phase-locked 3.7 GHz Oscillator output. The IF signal from the Band 0 Splitter/Detector is routed through the Switched-YIG-Tuned Multiplier (SYTM), the Band 1-4 Coupler, and the 90 dB Step Attenuator before reaching the RF OUTPUT connector. The SYTM and Band 1-4 Coupler perform no function in this band. Option 001 and 005 instruments do not have a Step Attenuator.

Band 1 (2.3 to 7.0 GHz) is the same as the YO frequency range. The RF from the Band 1-4 output on the Mod/Splitter is amplified by the Band 1-4 Power Amplifier and passes through the SYTM to the Band 1-4 Coupler. Here, part of the RF is coupled to the Band 1-4 Detector for leveling through the ALC Loop. After the coupler, the RF passes through the 90 dB Step Attenuator (on instruments so equipped) to the RF OUTPUT.

Bands 2-4 (7.0 to 26.5 GHz) are generated by multiplying the YO frequency in the SYTM. A Step Recovery Diode (SRD) in the SYTM, when biased properly, generates harmonics of the input signal. A YIG-Tuned filter tracks the desired harmonic allowing it to pass through to the Band 1-4 Coupler and Step Attenuator (if equipped with Step Attenuator) to the RF OUTPUT. The SYTM Driver provides the necessary circuitry so the YIG-Tuned filter in the SYTM can track the YO properly. Leveling in Bands 2-4 is the same as in Band 1.

Pulse modulation in the HP 8340A is produced by the Pulse Modulator Driver and two fast response time pulse modulators. The Band 0 Pulse Modulator, located just before the Band 0 Mixer, is used when the HP 8340A is operating below 2.3 GHz. Operation above 2.3 GHz uses the Band 1-4 Pulse Modulator inside the Mod/Splitter.

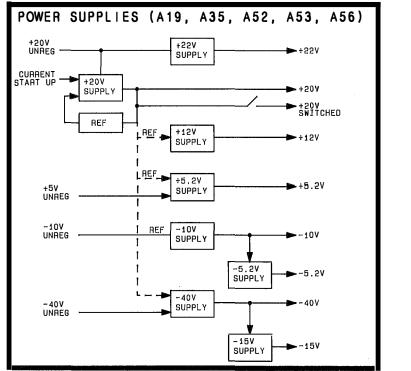

#### **POWER SUPPLIES**

The power supply in the HP 8340A produces eight regulated voltage levels, four positive supplies and four negative supplies. These voltages are +22, +20, +12, +5.2, -5.2, -10, -15, and -40 volts. The +22 volt supply powers the 10 MHz Reference Oscillator heater coil. This is the only supply that actually produces an output when the HP 8340A is switched to **STANDBY**. All supplies except for the +22 volt supply are referenced either directly or indirectly to the +20 volt supply. In **STANDBY** mode, the +20 volt supply shuts down. This in turn shuts down the regulators for all other supplies (except the +22 volt supply). However, it is important to note that even though these supplies are "shut down," all of the unregulated supply circuits are fully operational. Therefore, hazardous voltages exist in these sections of the instrument even when the front panel **POWER** switch is set to **STANDBY**. The +20, -15, -10, and -40 volt supplies deliver current to the low noise analog circuits and the microcircuits. The +12, +5.2, -5.2, and -15 volt supplies deliver power to the digital and non-critical analog circuits. Over temperature protection, current limit, and over voltage protection are built into each supply. The output voltage of each supply (excluding the +22 volt supply) is monitored. If any of these supplies drop out of regulation, the instrument microprocessor is flagged.

100

Ì

Figure 8A-2. Model 8340A Block Diagram 8-13/8-14

.

.

#### **CALIBRATION CONSTANTS**

#### Introduction

There are three sets of Calibration Constants maintained by the HP 8340A which contain the calibration data, serial number, option, HP-IB Address, and CHECKSUM information. The three sets of Calibration Constants are:

- \* Working Data

- \* Protected Data

- \* Default Data

Working Data contains the calibration information that is required for optimum performance of the HP 8340A. This is the only set of Calibration Constants that is accessed during normal operation of the HP 8340A. It is stored in RAM on the A60 Processor Assembly and maintained by battery A60BT1.

Protected Data contains calibration information which is accessed by the instrument if there is a problem with the Working Data or accessed by the user to update the data. The Protected Data is typically an exact duplicate of the Working Data and acts as a backup in the event an error occurs in the Working Data. Protected data is stored in EE-PROM on the A60 Processor Assembly.

Default Data differs from the Working and Protected Data in that its calibration data is the average calibration data of several HP 8340As. This is done to ensure that if any HP 8340A goes to Default Data, it will still be fairly close to its required calibration data for normal operation. This data is stored in UV-EPROM on the A60 Processor Assembly. The only instance where the instrument would select Default Data would be if a problem existed with both the Working and Protected Data.

#### **Instrument and User Access**

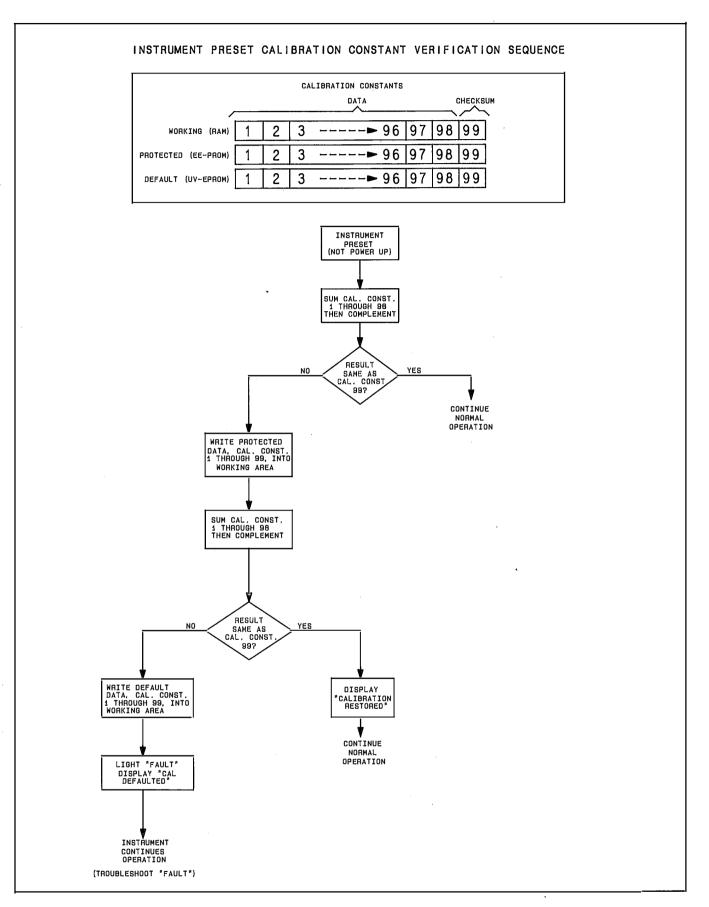

During normal operation, the HP 8340A will access the Working Data to obtain the calibration information required for optimum operation of the instrument. In addition to this, the HP 8340A will access the Working Data after an **[INSTR PRESET]** is initiated, and only to verify that the CHECKSUM (Cal Constant #99) is accurate (see Figure 8A-3, Instrument Preset Calibration Constant Verification Sequence).

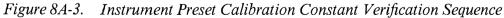

When **[INSTR PRESET]** is pressed, the Working Data Cal Constants 1 through 98 are summed and then complemented. The result is then compared with the CHECKSUM. If the two numbers agree, the instrument continues normal operation. If not, the Protected Data is written into the Working Data's memory location and the CHECKSUM test is repeated. If the checksum test passes, the data that was in Protected Data is now stored as Working and Protected Data and displayed in the ENTRY DISPLAY will be "CALIBRATION RESTORED." If the CHECKSUMs do not agree, the Default Data is then written to the Working Data. The Working Data now contains the Default values, the FAULT light on the HP 8340A front panel is lit, and "CAL DEFAULTED" is displayed. Pressing **[SHIFT] [MANUAL]** will display the FAULT diagnostics in the ENTRY DISPLAY and the CAL light will be flashing. (Note that the Protected Data was not changed. For troubleshooting, this data may be written into the Working Data (per procedure #5 below) and viewed (per procedure #1 below)).

## CAUTION

The following describes methods for intentionally changing the values of the Cal Constants. When a Cal Constant is changed, the CHECKSUM is automatically updated. If a CAL FAULT occurs and a Cal Constant is updated, on the next [INSTR PRESEST] (unless otherwise stated), the CAL FAULT indicator will turn off. This means that if only a few of the Cal Constants were updated, the balance will still be using Default Data.

A number of methods exist for user access of the Cal Constants. A description of each follows:

#### 1. CALIBRATION CONSTANT ACCESS

#### [SHIFT] [MHz] [1] [2] [Hz]

(I/O SUBCHANNEL: 12 displayed in ENTRY DISPLAY)

#### [SHIFT] [kHz] [2] [2] [Hz]

(I/O WRITE: 22 displayed in ENTRY DISPLAY)

Performing this key sequence allows the user direct access to the Working Data. At this point the data may either be viewed or changed. Immediately after entering the final [Hz], a Cal Constant number and value for that specific Cal Constant will be displayed on the HP 8340A ENTRY DISPLAY. Using the up and down [STEP] keys allows the rest of the Cal Constants to be viewed. For immediate access to a specific Cal Constant, press [SHIFT] [GHz] (I/O CHANNEL: XX displayed in ENTRY DISPLAY), enter the number of the desired Cal Constant, and then press [Hz] prior to beginning the above key sequence. To change a Cal Constant, use the [STEP] keys to move to the desired Cal Constant. Then use either the RPG or the ENTRY keyboard to enter a new value. After the desired value is reached, press [Hz]. At this point the Cal Constant value is changed and the CHECKSUM is updated. Note that using this method only changes the Working Data. To permanently change the Protected Data, the procedure described in #4 must be followed.

#### 2. HP-IB ADDRESS ACCESS

#### [SHIFT] [LOCAL]

Performing this key sequency allows the HP-IB address to be viewed in the ENTRY DISPLAY. By rotating the RPG or by keyboard entry, the HP-IB address may be changed from 00 to 30. When the desired address is set, press the **[Hz]** key and the HP-IB address will be changed and the CHECKSUM updated (note that only the Working Data is updated). To prevent the HP-IB address from being changed in this manner, bit 5 of Cal Constant #57 may be set and this function is disallowed. The procedure for doing this is:

- a. Access the Working Data Cal Constant #57 as described in #1.

- b. Set bit 5 by adding 32 to the HP-IB address. Enter this value.

- c. Press [Hz].

- 3. AUTOMATIC SYTM TO YTO TRACKING (POWER OPTIMIZATION)

#### [SHIFT] [PEAK]

Performing this key sequence causes an automatic SYTM Tracking to be performed. This function automatically adjusts and updates the YTM GAIN Cal Constants (#9 through #12 and #50 through #53) for peak RF output power and then updates the CHECKSUM. This function will also automatically turn off the CAL FAULT indicator without performing an **[INSTR PRESET]** as described in the above note.

4. WORKING DATA TO PROTECTED DATA TRANSFER

| [SHIFT] | [MHz] | [1] | [4] | [Hz] |      |

|---------|-------|-----|-----|------|------|

| [SHIFT] |       |     |     |      | [Hz] |

Performing this key sequence causes the CHECKSUM of the Working Data to be recalculated and stored. The Working Data is then written over the Protected Data and stored as Protected Data. This is the only method for updating the Protected Data. If this transfer of data fails, the message "EEROM FAILURE, CAL NOT STORED" will be displayed in the ENTRY DISPLAY. 5. PROTECTED DATA TO WORKING DATA TRANSFER

[SHIFT] [MHz] [1] [4] [Hz] [SHIFT] [kHz] [1] [9] [4] [6] [Hz]

Performing this key sequence causes the HP 8340A to recall the Protected Data and store it in the Working Data memory location.

6. SAVE/RECALL REGISTER INITIALIZATION

| [SHIFT] | [MHz] | [1] | [8]  |

|---------|-------|-----|------|

| [SHIFT] | [kHz] | [0] | [Hz] |

Performing this key sequence, switching the HP 8340A off then on, and then pressing **[INSTR PRESET]** forces the HP 8340A to reinitialize the Save/Recall Registers in RAM (this function does not effect the Cal Constants).

7. CAL CONSTANTS PASSWORD ENABLE

| [SHIFT] | [GHz] | [8] | [2] | [Hz] |      |

|---------|-------|-----|-----|------|------|

| [SHIFT] | [MHz] | [1] | [2] | [Hz] |      |

| [SHIFT] | [kHz] | [2] | [2] | [Hz] |      |

| [-] [2  | ] [3] | [8] | [7] | [5]  | [Hz] |

The above key sequence accesses Cal Constant number 82 (LOCKWORD ENABLE) and sets it to -23,875. This enables the lockword function and sets Cal Constant number 81 (LOCKWORD) to 0. To change the LOCKWORD (password), access Cal Constant number 81 by pressing the down arrow STEP key. Enter a number between -32,768 and 32,767 via the ENTRY keyboard and terminate the entry with **[Hz]**. The number entered will be the password required to access the calibration constants. After this, remove number A59W1 on the A59 Digital Interface assembly. This is the final step in enabling the Cal Constants' lockword function. In the event that the password is forgotten, re-installing jumper A59W1 will disable the lockword function.

8. CALIBRATION CONSTANT ACCESS WHEN LOCKWORD FUNCTION IS ENABLED

### [SHIFT] [MHz] [2] [0] [Hz]

This key sequence allows access to the location (sub-channel) where the password for access to the Cal Constants will need to be entered. After pressing the above key sequence, enter the password via the ENTRY keyboard and press **[Hz]**. Upon entry of the correct password, the Cal Constants may be accessed per procedure #1 described previously.

#### Description

A listing and description of the Cal Constants is given in Table 8A-3. The values that are given in the "Range" column represent the amount of adjustment that is possible with the Cal Constant. The numbers that are shown are the only ones that should be entered by the user. It is possible to enter values out of the given range, but they will not represent the value being used by the HP 8340A. The column labeled "Significance" gives the units associated with the Cal Constant. For example, the value entered for DWELL TIME represents the number of milliseconds that the HP 8340A will wait, after phase lock at the beginning of a sweep or at bandcross, before it will continue its sweep. Another example is the 9GZ SLOPE. For each count, a power compensation of 0.0025 dB/GHz will be added to the RF output. In other words, if 10 were entered for the Cal Constant, a 0.025 dB/GHz slopoe (10 times 0.0025 dB/GHz) would be added for a sweep within the 9 to 20 GHz range.

Five of the Cal Constants, PRESET OPTION (#56), HPIB ADDRESS (#57), RETRACE DWELL (#58), ATTEN CONFIG (#59), and CONFIGURATION (#60) use their bit configuration to store more than one piece of information for the HP 8340A. For example, the HPIB ADDRESS sets up the HP 8340A's HP-IB address and allows or disallows the [SHIFT] [LOCAL], [SHIFT] [SAVE], and [SHIFT] [RECALL] functions. If a user wished to set up an HP-IB address of 19, disallow the [SHIFT] [LOCAL] and [RECALL] functions, and allow the [SHIFT] [SAVE] function, the user would enter 179 for Cal Constant #57. The 179 was arrived at by adding 19 (HP-IB address), 32 (disallows [SHIFT][ LOCAL]), 0 (allows [SHIFT] [SAVE]), and 128 (disallows [SHIFT] [RECALL]). The other four Cal Constants work in the same manner.

A hard copy of the HP 8340A's Protected Data is included in a plastic envelope with each instrument. It is stored in a bracket which is located underneath the top cover, on the side of the instrument. If the Working and Protected Data are ever lost, the information on this sheet should be used to restore the Cal Constants. Also, when the HP 8340A is recalibrated, the hard copy of the Protected Data should be updated and placed back into the instrument (remember to update the Protected Data). A sample of the hard copy that is included with the instrument is shown in Figure 8A-4.

| 8340A CALIBRATION CONSTANTS<br>SERIAL NUMBER; 9999 8340AREV 08 JAN 85                                                                                                                        |                                                             |                                     |                                                                                                                     |                      |              |              |                               |        |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------|--------------|--------------|-------------------------------|--------|---|

| ==========                                                                                                                                                                                   |                                                             |                                     | =========                                                                                                           |                      | = =          | ==           |                               |        | - |

| 1. DWELL TIME                                                                                                                                                                                | 50                                                          |                                     | 4. AT90 SLOPE                                                                                                       | -12                  |              |              | AT60 SLP 20GZ                 | 10     |   |

| 2. YTM BX DLY 2                                                                                                                                                                              |                                                             |                                     | 5. unused                                                                                                           | 0                    |              |              | AT70 SLP 20GZ                 | 13     | I |

| 3. YTM BX DLY 3                                                                                                                                                                              | 131                                                         |                                     | 6. unused                                                                                                           | 0                    | II           |              | AT80 SLP 20GZ                 | 13     | 1 |

| 4. YTM BX DLY 4                                                                                                                                                                              |                                                             |                                     | 7. unused                                                                                                           | 0                    | II           |              | AT90 SLP 20GZ                 | 18     |   |

| 5. YTM DLY 1                                                                                                                                                                                 | 89                                                          |                                     | 8. unused                                                                                                           | 0                    | 11           |              | YTM OFFSET 1                  | 1024   |   |

| 6. YTM DLY 2                                                                                                                                                                                 | 100                                                         |                                     | 9. ADC GAIN LO                                                                                                      |                      | . 11         |              | YTM OFFSET 2                  | 1024   |   |

| 7. YTM DLY 3                                                                                                                                                                                 |                                                             |                                     | 0. ADC GAIN HI                                                                                                      | -28                  |              |              | YTM OFFSET 3                  | 1024   | 1 |

| 8. YTM DLY 4                                                                                                                                                                                 |                                                             |                                     | 1. MAX SWEEP RATE                                                                                                   | 600                  |              |              | YTM OFFSET 4                  | 1024   |   |

| 9. YTM GAIN 1                                                                                                                                                                                |                                                             |                                     | 2. ADC OFFSET                                                                                                       | -36                  |              |              | YTM TC GAIN                   | 25     |   |

| 10. YTM GAIN 2                                                                                                                                                                               |                                                             |                                     | 3. AM OFFSET                                                                                                        | 0                    |              |              | YTM TC OFFSET                 | 1000   |   |

| 11. YTM GAIN 3                                                                                                                                                                               | =                                                           |                                     | 4. LVL DAC OFF; INT                                                                                                 | 33                   |              |              | YTM TC BKP GAIN               | 175    |   |

| 12. YTM GAIN 4                                                                                                                                                                               |                                                             |                                     | 5. LVL DAC OFF; EXT                                                                                                 | 2                    | 11           |              | YTM TC BKP FREQ               | 50     |   |

| 13. LO SLOPE                                                                                                                                                                                 |                                                             |                                     | 6. LVL DAC GAIN; LO                                                                                                 | 8                    |              |              | OI MODEL                      | 1      |   |

| 14. HI SLOPE                                                                                                                                                                                 |                                                             |                                     | 7. LVL DAC GAIN; HI                                                                                                 | 3                    |              |              | unused                        | 0      |   |

| 15. 9GZ SLOPE                                                                                                                                                                                | 100                                                         |                                     | 8. LVL DAC GAIN; EXT                                                                                                |                      | II           |              | LOCKWORD                      | 0      |   |

| 16. 20GZ SLOPE                                                                                                                                                                               |                                                             |                                     | 9. PWR SWP GAIN                                                                                                     | 1                    |              |              | LOCKWORD ENABL                |        |   |

| 17. AT10 OFFSET                                                                                                                                                                              | -                                                           |                                     | 0. YTM BX GAIN 1                                                                                                    | 890                  |              |              | unused                        | 0      |   |

| 18. AT20 OFFSET                                                                                                                                                                              | -5                                                          |                                     | 1. YTM BX GAIN 2                                                                                                    | 791                  | 11           |              | unused                        | 0      |   |

| 19. AT30 OFFSET                                                                                                                                                                              | -1                                                          |                                     | 2. YTM BX GAIN 3                                                                                                    | 1030                 | 11           |              | unused                        | 0      |   |

| 1 20. AT40 OFFSET                                                                                                                                                                            | -4                                                          |                                     | 3. YTM BX GAIN 4                                                                                                    | 990                  |              |              | unused                        | 0      |   |

| 21. AT50 OFFSET                                                                                                                                                                              | -7                                                          |                                     | 4. STOP LIMIT                                                                                                       | 20000                |              |              | unused                        | 0      |   |

| 22. AT60 OFFSET                                                                                                                                                                              | -2                                                          |                                     | 5. START LIMIT                                                                                                      | 10                   |              |              | unused                        | 0      |   |

| 23. AT70 OFFSET                                                                                                                                                                              | -5                                                          |                                     | 6. PRESET OPTION                                                                                                    | 0                    |              |              | unused                        | 0      |   |

| 24. AT80 OFFSET                                                                                                                                                                              |                                                             |                                     | 7. HPIB ADDRESS                                                                                                     | 531                  |              |              | unused                        | 0      |   |

| 25. AT90 OFFSET                                                                                                                                                                              | -10                                                         |                                     | 8. RETRACE DWELL                                                                                                    | 0                    |              |              | unused                        | 0      |   |

| 26. AT10 SLOPE                                                                                                                                                                               | -2                                                          |                                     | 9. ATTEN CONFIG                                                                                                     | 20980                |              |              | unused                        | 0      |   |

| 27. AT20 SLOPE                                                                                                                                                                               | -4                                                          |                                     | 0. CONFIGURATION                                                                                                    | 23                   |              |              | unused                        | 0      |   |

| 28. AT30 SLOPE                                                                                                                                                                               | -3                                                          |                                     | 1. SERIAL #                                                                                                         | 9999                 | 11           |              | unused                        | 0      |   |

| 29. AT40 SLOPE                                                                                                                                                                               | -5                                                          |                                     | 2. AT10 SLP 20GZ                                                                                                    | 4                    | 1            |              | unused                        | 0      |   |

| 30. AT50 SLOPE                                                                                                                                                                               | -7                                                          |                                     | 3. AT20 SLP 20GZ                                                                                                    | 5                    | 1            |              | unused                        | 0      | - |

| 31. AT60 SLOPE                                                                                                                                                                               |                                                             |                                     | 4. AT30 SLP 20GZ                                                                                                    | 5                    |              |              | unused                        | 0      |   |

| 32. AT70 SLOPE                                                                                                                                                                               | -                                                           |                                     | 5. AT40 SLP 20GZ                                                                                                    | 8                    |              |              | MODEL #                       | 0      |   |

| 33. AT80 SLOPE                                                                                                                                                                               | -10                                                         | 11 6                                | 6. AT50 SLP 20GZ                                                                                                    | 9                    | П            | 99.          | CHECKSUM                      | 9557   | ' |

|                                                                                                                                                                                              |                                                             |                                     |                                                                                                                     |                      | - =<br>- =   | ==           |                               |        | _ |

| <ol> <li>Procedure for manually enture</li> <li>Push the following sequence</li> <li>Instrument Preset SI</li> <li>Note the Entry Display</li> <li>Enter via the KEY BOA display.</li> </ol> | ering cali<br>ience of l<br>HIFT MI<br>will indi<br>RD or D | brati<br>KEY<br>Hz 1<br>cate<br>ATA | on data into the HP 8340/<br>S:<br>2 Hz SHIFT KHz 2 2 H<br>the Calibration Constant 1<br>KNOB the correct value for | A:<br>Hz<br>1umber a | ınd          | valu         | e.                            |        |   |

| 4. Go to the next Calibrati<br>enter the "CHECKS                                                                                                                                             | on Const<br>UM" Co                                          | ant l<br>nsta                       | es with the Hz key $\gg$<br>by pushing the UP step key<br>at. (This is computed auto                                | matically            | y)           |              |                               |        |   |

| them.                                                                                                                                                                                        |                                                             |                                     | om one Calibration Const                                                                                            |                      |              |              |                               |        |   |

| 6. After all entries have be them.                                                                                                                                                           | en made                                                     | , cne                               | ck that all numbers are con                                                                                         | rect by u            | 15111        | g ine        | step keys to review and       | verity |   |

| 7. Allow instrument to wa<br>on the rear panel. Pu<br>the "YTM GAIN n"                                                                                                                       | sh SHIF<br>' & "YTN                                         | ГРЕ<br>ИВУ                          |                                                                                                                     | tic Track            | ing          | Cal          | ibration. This step may n     | nodify |   |

| 8. The CALIBRATION d<br>following key sequer                                                                                                                                                 | ata shoul<br>nce: SHIF                                      | d be<br>FT N                        | bermanently stored in the<br>Hz 14 Hz SHIFT KHz                                                                     | Non Vola<br>5349 Hz  | atile<br>z P | e Pro<br>RES | tected Memory by pushi<br>ET. | ng the |   |

Figure 8A-4. Sample Calibration Constants Hard Copy (Found Inside Instrument)

8-20

.

Ì

| No. | Name         | Function                                                                                                    | Range<br>(Counts) | Significance                        |  |  |  |  |  |  |

|-----|--------------|-------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------|--|--|--|--|--|--|

| 1   | DWELL TIME   | Defines time to wait after phase lock at beginning of sweep and at bandcross.                               | 0-500             | 0.2 ms/count                        |  |  |  |  |  |  |

| 2   | YTM BX DLY 2 | Compensates for YTM Delay in Band 2 after bandcross from Band 1 to Band 2.                                  | 0-131             | 2.4 MHz/ms/count                    |  |  |  |  |  |  |

| 3   | YTM BX DLY 3 | Compensates for YTM Delay in Band 3 after bandcross from Band 2 to Band 3.                                  | 0-131             | 2.4 MHz/ms/count                    |  |  |  |  |  |  |

| 4   | YTM BX DLY 4 | Compensates for YTM Delay in Band 4 after bandcross from Band 3 to Band 4.                                  | 0-131             | 2.4 MHz/ms/count                    |  |  |  |  |  |  |

| 5   | YTM DLY 1    | Compensates for YTM Delay in Band 1.                                                                        | 0-131             | 2.4 MHz/ms/count                    |  |  |  |  |  |  |

| 6   | YTM DLY 2    | Compensates for YTM Delay in Band 2<br>for single band sweeps or multi-band<br>sweeps that begin in Band 2. | 0-131             | 2.4 MHz/ms/count                    |  |  |  |  |  |  |

| 7   | YTM DLY 3    | Compensates for YTM Delay in Band 3 for single band sweeps or multi-band sweeps that begin in Band 3.       | 0-131             | 2.4 MHz/ms/count                    |  |  |  |  |  |  |

| 8   | YTM DLY 4    | Compensates for YTM Delay in Band 4 for single band sweep.                                                  | 0-131             | 2.4 MHz/ms/count                    |  |  |  |  |  |  |

| 9   | YTM GAIN 1   | Adjusts Band 1 in YTM slow speed tracking.                                                                  | 0-2040            | -4% - +4% of<br>YTM Frequency       |  |  |  |  |  |  |

| 10  | YTM GAIN 2   | Adjusts Band 2 YTM slow speed tracking.                                                                     | 0-2040            | -2% - +2% of<br>YTM Frequency       |  |  |  |  |  |  |

| 11  | YTM GAIN 3   | Adjusts Band 3 YTM slow speed tracking.                                                                     | 0-2040            | -1.33% - +1.33%<br>of YTM Frequency |  |  |  |  |  |  |

| 12  | YTM GAIN 4   | Adjusts Band 4 YTM slow speed tracking                                                                      | 0-2040            | -1% - +1% of<br>YTM Frequency       |  |  |  |  |  |  |

| 13  | LO SLOPE     | Slope compensation for RF power in Band 0.                                                                  | 0-255             | 0.005 dB/GHz/count                  |  |  |  |  |  |  |

| 14  | HI SLOPE     | Slope compensation for RF power from 2.3 to 9.0 GHz.                                                        | 0-255             | 0.005 dB/GHz/count                  |  |  |  |  |  |  |

| 15  | 9 GZ SLOPE   | Slope compensation for RF power from 9.0 to 20.0 GHz.                                                       | 0-255             | 0.0025 dB/GHz/count                 |  |  |  |  |  |  |

| 16  | 20 GZ SLOPE  | Slope compensation for RF power from 20.0 to 26.5 GHz.                                                      | 0-255             | 0.01 dB/GHz/count                   |  |  |  |  |  |  |

| 17  | AT10 OFFSET  | Offset compensation for RF power at 10 dB attenuator setting from 0.01 to 26.5 GHz.                         | -200 -<br>+200    | 0.05 dB/count                       |  |  |  |  |  |  |

## Table 8A-3. Calibration Constants (1 of 7)

|      | l           | I                                                                                         |                   |                    |

|------|-------------|-------------------------------------------------------------------------------------------|-------------------|--------------------|

| No.  | Name        | Function                                                                                  | Range<br>(Counts) | Significance       |

| 18   | AT20 OFFSET | Offset compensation for RF power at 20 dB attenuator setting from 0.01 to 26.5 GHz.       | -200 -<br>+200    | 0.05 dB/count      |

| 19   | AT30 OFFSET | Offset compensation for RF power at 30 dB attenuator setting from 0.01 to 26.5 GHz.       | 200 -<br>+200     | 0.05 dB/count      |

| 20   | AT40 OFFSET | Offset compensation for RF power at 40 dB attenuator setting from 0.01 to 26.5 GHz.       | -200 -<br>+200    | 0.05 dB/count      |

| 21   | AT50 OFFSET | Offset compensation for RF power at 50 dB attenuator setting from 0.01 to 26.5 GHz.       | -200 -<br>+200    | 0.05 dB/count      |

| 22   | AT60 OFFSET | Offset compensation for RF power at 60 dB attenuator setting from 0.01 to 26.5 GHz.       | -200 -<br>+200    | 0.05 dB/count      |

| 23   | AT70 OFFSET | Offset compensation for RF power at 70<br>dB attenuator setting from 0.01 to 26.5<br>GHz. | -200 -<br>+200    | 0.05 dB/count      |

| 24   | AT80 OFFSET | Offset compensation for RF power at 80 dB attenuator setting from 0.01 to 26.5 GHz.       | -200 + 200        | 0.05 dB/count      |

| 25   | AT90 OFFSET | Offset compensation for RF power at 90 dB attenuator setting from 0.01 to 26.5 GHz.       | -200 + 200        | 0.05 dB/count      |

| 26   | AT10 SLOPE  | Slope compensation for RF power at 10 dB attenuator setting from 2.3 to 20.0 GHz.         | -255 -<br>+255    | 0.005 dB/GHz/count |

| 27 · | AT20 SLOPE  | Slope compensation for RF power at 20<br>dB attenuator setting from 2.3 to 20.0<br>GHz.   |                   | 0.005 dB/GHz/count |

| 28   | AT30 SLOPE  | Slope compensation for RF power at 30 dB attenuator setting from 2.3 to 20.0 GHz.         | -255 -<br>+255    | 0.005 dB/GHz/count |

| 29   | AT40 SLOPE  | Slope compensation for RF power at 40 dB attenuator setting from 2.3 to 20.0 GHz.         | -255 -<br>+255    | 0.005 dB/GHz/count |

| 30   | AT50 SLOPE  | Slope compensation for RF POWER at 50 dB attenuator setting from 2.3 to 20.0 GHz.         | -255 -<br>+255    | 0.005 dB/GHz/count |

## Table 8A-3.Calibration Constants (2 of 7)

4

,